mirror of

https://github.com/RIOT-OS/RIOT.git

synced 2024-12-29 04:50:03 +01:00

Merge pull request #14662 from benpicco/cpu/samd20

cpu/samd21: add support for SAMD20 & SAM D20 Xplained Pro board

This commit is contained in:

commit

98726ded6d

22

boards/samd20-xpro/Kconfig

Normal file

22

boards/samd20-xpro/Kconfig

Normal file

@ -0,0 +1,22 @@

|

||||

# Copyright (c) 2020 HAW Hamburg

|

||||

#

|

||||

# This file is subject to the terms and conditions of the GNU Lesser

|

||||

# General Public License v2.1. See the file LICENSE in the top level

|

||||

# directory for more details.

|

||||

|

||||

config BOARD

|

||||

default "samd20-xpro" if BOARD_SAMD20_XPRO

|

||||

|

||||

config BOARD_SAMD20_XPRO

|

||||

bool

|

||||

default y

|

||||

select CPU_MODEL_SAMD20J18

|

||||

select HAS_PERIPH_ADC

|

||||

select HAS_PERIPH_DAC

|

||||

select HAS_PERIPH_I2C

|

||||

select HAS_PERIPH_PWM

|

||||

select HAS_PERIPH_RTC

|

||||

select HAS_PERIPH_RTT

|

||||

select HAS_PERIPH_SPI

|

||||

select HAS_PERIPH_TIMER

|

||||

select HAS_PERIPH_UART

|

||||

3

boards/samd20-xpro/Makefile

Normal file

3

boards/samd20-xpro/Makefile

Normal file

@ -0,0 +1,3 @@

|

||||

MODULE = board

|

||||

|

||||

include $(RIOTBASE)/Makefile.base

|

||||

3

boards/samd20-xpro/Makefile.dep

Normal file

3

boards/samd20-xpro/Makefile.dep

Normal file

@ -0,0 +1,3 @@

|

||||

ifneq (,$(filter saul_default,$(USEMODULE)))

|

||||

USEMODULE += saul_gpio

|

||||

endif

|

||||

13

boards/samd20-xpro/Makefile.features

Normal file

13

boards/samd20-xpro/Makefile.features

Normal file

@ -0,0 +1,13 @@

|

||||

CPU = samd21

|

||||

CPU_MODEL = samd20j18

|

||||

|

||||

# Put defined MCU peripherals here (in alphabetical order)

|

||||

FEATURES_PROVIDED += periph_adc

|

||||

FEATURES_PROVIDED += periph_dac

|

||||

FEATURES_PROVIDED += periph_i2c

|

||||

FEATURES_PROVIDED += periph_pwm

|

||||

FEATURES_PROVIDED += periph_rtc

|

||||

FEATURES_PROVIDED += periph_rtt

|

||||

FEATURES_PROVIDED += periph_spi

|

||||

FEATURES_PROVIDED += periph_timer

|

||||

FEATURES_PROVIDED += periph_uart

|

||||

1

boards/samd20-xpro/Makefile.include

Normal file

1

boards/samd20-xpro/Makefile.include

Normal file

@ -0,0 +1 @@

|

||||

include $(RIOTMAKE)/boards/sam0.inc.mk

|

||||

35

boards/samd20-xpro/board.c

Normal file

35

boards/samd20-xpro/board.c

Normal file

@ -0,0 +1,35 @@

|

||||

/*

|

||||

* Copyright (C) 2020 ML!PA Consulting GmbH

|

||||

*

|

||||

* This file is subject to the terms and conditions of the GNU Lesser

|

||||

* General Public License v2.1. See the file LICENSE in the top level

|

||||

* directory for more details.

|

||||

*/

|

||||

|

||||

/**

|

||||

* @ingroup boards_samd20-xpro

|

||||

* @{

|

||||

*

|

||||

* @file

|

||||

* @brief Board specific implementations for the Atmel SAM D20 Xplained

|

||||

* Pro board

|

||||

*

|

||||

* @author Benjamin Valentin <benjamin.valentin@ml-pa.com>

|

||||

* @}

|

||||

*/

|

||||

|

||||

#include "board.h"

|

||||

#include "periph/gpio.h"

|

||||

|

||||

void board_init(void)

|

||||

{

|

||||

/* initialize the on-board LED */

|

||||

gpio_init(LED0_PIN, GPIO_OUT);

|

||||

LED0_OFF;

|

||||

|

||||

/* initialize the on-board button */

|

||||

gpio_init(BTN0_PIN, BTN0_MODE);

|

||||

|

||||

/* initialize the CPU */

|

||||

cpu_init();

|

||||

}

|

||||

2

boards/samd20-xpro/dist/openocd.cfg

vendored

Normal file

2

boards/samd20-xpro/dist/openocd.cfg

vendored

Normal file

@ -0,0 +1,2 @@

|

||||

source [find target/at91samdXX.cfg]

|

||||

$_TARGETNAME configure -rtos auto

|

||||

85

boards/samd20-xpro/doc.txt

Normal file

85

boards/samd20-xpro/doc.txt

Normal file

@ -0,0 +1,85 @@

|

||||

/**

|

||||

@defgroup boards_samd20-xpro Atmel SAM D20 Xplained Pro

|

||||

@ingroup boards

|

||||

@brief Support for the Atmel SAM D20 Xplained Pro board.

|

||||

|

||||

## Overview

|

||||

|

||||

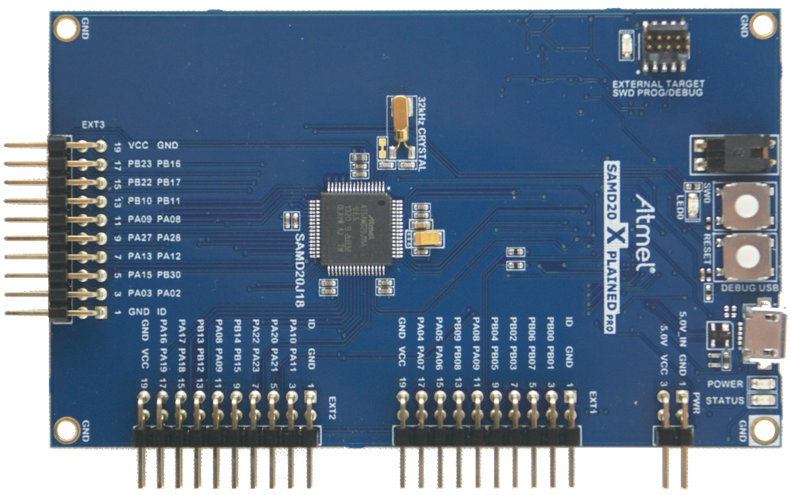

The `SAMD20 Xplained Pro` is an ultra-low power evaluation board by Atmel

|

||||

featuring an ATSAMD20J18 SoC. The SoC includes a SAMD20 ARM Cortex-M0+ micro-

|

||||

controller. For programming the MCU comes with 32Kb of RAM and 256Kb of flash

|

||||

memory.

|

||||

|

||||

## Hardware

|

||||

|

||||

|

||||

|

||||

|

||||

### MCU

|

||||

| MCU | ATSAMD20J18A |

|

||||

|:-------------- |:--------------------------------- |

|

||||

| Family | ARM Cortex-M0+ |

|

||||

| Vendor | Atmel |

|

||||

| RAM | 32 KiB |

|

||||

| Flash | 256 KiB |

|

||||

| Frequency | up to 48MHz |

|

||||

| FPU | no |

|

||||

| Timers | 8 (16-bit) |

|

||||

| ADCs | 1x 12-bit (20 channels) |

|

||||

| UARTs | max 6 (shared with SPI and I2C) |

|

||||

| SPIs | max 6 (see UART) |

|

||||

| I2Cs | max 6 (see UART) |

|

||||

| Vcc | 1.62V - 3.63V |

|

||||

| Datasheet | [Datasheet](http://ww1.microchip.com/downloads/en/DeviceDoc/SAM_D20_%20Family_Datasheet_DS60001504C.pdf) |

|

||||

| Board Manual | [Board Manual](http://ww1.microchip.com/downloads/en/DeviceDoc/Atmel-42102-SAMD20-Xplained-Pro_User-Guide.pdf)|

|

||||

|

||||

### User Interface

|

||||

|

||||

1 User button and 1 LED:

|

||||

|

||||

| Device | PIN |

|

||||

|:------------- |:----- |

|

||||

| LED0 | PA14 |

|

||||

| SW0 (button) | PA15 |

|

||||

|

||||

## Flashing the device

|

||||

|

||||

Connect the device to your Micro-USB cable using the port labeled as *DEBUG

|

||||

USB*.

|

||||

|

||||

The standard method for flashing RIOT to the samd20-xpro is using OpenOCD.

|

||||

|

||||

Refer to https://github.com/RIOT-OS/RIOT/wiki/OpenOCD for general

|

||||

instructions on building OpenOCD and make sure "cmsis-dap" and "hidapi-libusb"

|

||||

are enabled.

|

||||

|

||||

On Linux you will have to add a **udev** rule for hidraw, like

|

||||

```

|

||||

bash

|

||||

echo 'KERNEL=="hidraw*", SUBSYSTEM=="hidraw", MODE="0664", GROUP="plugdev"' \

|

||||

| sudo tee -a /etc/udev/rules.d/99-usb.rules

|

||||

sudo service udev restart

|

||||

```

|

||||

|

||||

### Arch Linux

|

||||

With yaourt:

|

||||

```

|

||||

yaourt -S hidapi-git

|

||||

yaourt -S openocd-git

|

||||

# edit PKGBUILD, add "cmsis-dap hidapi-libusb" to "_features"

|

||||

```

|

||||

|

||||

### Ubuntu

|

||||

Although this refers to setting up the SAMR21, this guide is still very

|

||||

helpful to understanding how to set up a solid RIOT development environment for

|

||||

the SAMD20: http://watr.li/samr21-dev-setup-ubuntu.html

|

||||

|

||||

## Supported Toolchains

|

||||

|

||||

For using the samd20-xpro board we strongly recommend the usage of the

|

||||

[GNU Tools for ARM Embedded Processors](https://launchpad.net/gcc-arm-embedded)

|

||||

toolchain.

|

||||

|

||||

## Known Issues / Problems

|

||||

|

||||

*/

|

||||

72

boards/samd20-xpro/include/board.h

Normal file

72

boards/samd20-xpro/include/board.h

Normal file

@ -0,0 +1,72 @@

|

||||

/*

|

||||

* Copyright (C) 2020 ML!PA Consulting GmbH

|

||||

*

|

||||

* This file is subject to the terms and conditions of the GNU Lesser

|

||||

* General Public License v2.1. See the file LICENSE in the top level

|

||||

* directory for more details.

|

||||

*/

|

||||

|

||||

/**

|

||||

* @ingroup boards_samd20-xpro

|

||||

* @{

|

||||

*

|

||||

* @file

|

||||

* @brief Board specific definitions for the Atmel SAM D20 Xplained Pro

|

||||

* board

|

||||

*

|

||||

* @author Benjamin Valentin <benjamin.valentin@ml-pa.com>

|

||||

*/

|

||||

|

||||

#ifndef BOARD_H

|

||||

#define BOARD_H

|

||||

|

||||

#include "cpu.h"

|

||||

#include "periph_conf.h"

|

||||

#include "periph_cpu.h"

|

||||

|

||||

#ifdef __cplusplus

|

||||

extern "C" {

|

||||

#endif

|

||||

|

||||

/**

|

||||

* @name xtimer configuration

|

||||

* @{

|

||||

*/

|

||||

#define XTIMER_DEV TIMER_DEV(0)

|

||||

#define XTIMER_CHAN (0)

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name LED pin definitions and handlers

|

||||

* @{

|

||||

*/

|

||||

#define LED0_PIN GPIO_PIN(PA, 14)

|

||||

|

||||

#define LED_PORT PORT->Group[PA]

|

||||

#define LED0_MASK (1 << 14)

|

||||

|

||||

#define LED0_ON (LED_PORT.OUTCLR.reg = LED0_MASK)

|

||||

#define LED0_OFF (LED_PORT.OUTSET.reg = LED0_MASK)

|

||||

#define LED0_TOGGLE (LED_PORT.OUTTGL.reg = LED0_MASK)

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name SW0 (Button) pin definitions

|

||||

* @{

|

||||

*/

|

||||

#define BTN0_PORT PORT->Group[PA]

|

||||

#define BTN0_PIN GPIO_PIN(PA, 15)

|

||||

#define BTN0_MODE GPIO_IN_PU

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @brief Initialize board specific hardware, including clock, LEDs and std-IO

|

||||

*/

|

||||

void board_init(void);

|

||||

|

||||

#ifdef __cplusplus

|

||||

}

|

||||

#endif

|

||||

|

||||

#endif /* BOARD_H */

|

||||

/** @} */

|

||||

53

boards/samd20-xpro/include/gpio_params.h

Normal file

53

boards/samd20-xpro/include/gpio_params.h

Normal file

@ -0,0 +1,53 @@

|

||||

/*

|

||||

* Copyright (C) 2020 ML!PA Consulting GmbH

|

||||

*

|

||||

* This file is subject to the terms and conditions of the GNU Lesser

|

||||

* General Public License v2.1. See the file LICENSE in the top level

|

||||

* directory for more details.

|

||||

*/

|

||||

|

||||

/**

|

||||

* @ingroup boards_samd20-xpro

|

||||

* @{

|

||||

*

|

||||

* @file

|

||||

* @brief Board specific configuration of direct mapped GPIOs

|

||||

*

|

||||

* @author Benjamin Valentin <benjamin.valentin@ml-pa.com>

|

||||

*/

|

||||

|

||||

#ifndef GPIO_PARAMS_H

|

||||

#define GPIO_PARAMS_H

|

||||

|

||||

#include "board.h"

|

||||

#include "saul/periph.h"

|

||||

|

||||

#ifdef __cplusplus

|

||||

extern "C" {

|

||||

#endif

|

||||

|

||||

/**

|

||||

* @brief GPIO pin configuration

|

||||

*/

|

||||

static const saul_gpio_params_t saul_gpio_params[] =

|

||||

{

|

||||

{

|

||||

.name = "LED(orange)",

|

||||

.pin = LED0_PIN,

|

||||

.mode = GPIO_OUT,

|

||||

.flags = SAUL_GPIO_INVERTED,

|

||||

},

|

||||

{

|

||||

.name = "Button(SW0)",

|

||||

.pin = BTN0_PIN,

|

||||

.mode = BTN0_MODE,

|

||||

.flags = SAUL_GPIO_INVERTED,

|

||||

},

|

||||

};

|

||||

|

||||

#ifdef __cplusplus

|

||||

}

|

||||

#endif

|

||||

|

||||

#endif /* GPIO_PARAMS_H */

|

||||

/** @} */

|

||||

317

boards/samd20-xpro/include/periph_conf.h

Normal file

317

boards/samd20-xpro/include/periph_conf.h

Normal file

@ -0,0 +1,317 @@

|

||||

/*

|

||||

* Copyright (C) 2020 ML!PA Consulting GmbH

|

||||

*

|

||||

* This file is subject to the terms and conditions of the GNU Lesser

|

||||

* General Public License v2.1. See the file LICENSE in the top level

|

||||

* directory for more details.

|

||||

*/

|

||||

|

||||

/**

|

||||

* @ingroup boards_samd20-xpro

|

||||

* @{

|

||||

*

|

||||

* @file

|

||||

* @brief Configuration of CPU peripherals for the Atmel SAM D20 Xplained

|

||||

* Pro board

|

||||

*

|

||||

* @author Travis Griggs <travisgriggs@gmail.com>

|

||||

* @author Dan Evans <photonthunder@gmail.com>

|

||||

* @author Benjamin Valentin <benjamin.valentin@ml-pa.com>

|

||||

*/

|

||||

|

||||

#ifndef PERIPH_CONF_H

|

||||

#define PERIPH_CONF_H

|

||||

|

||||

#include <stdint.h>

|

||||

|

||||

#include "cpu.h"

|

||||

#include "periph_cpu.h"

|

||||

|

||||

#ifdef __cplusplus

|

||||

extern "C" {

|

||||

#endif

|

||||

|

||||

/**

|

||||

* @name External oscillator and clock configuration

|

||||

*

|

||||

* There are three choices for selection of CORECLOCK:

|

||||

*

|

||||

* - usage of the 48 MHz DFLL fed by external oscillator running at 32 kHz

|

||||

* - usage of the PLL fed by the internal 8MHz oscillator divided by 8

|

||||

* - usage of the internal 8MHz oscillator directly, divided by N if needed

|

||||

*

|

||||

*

|

||||

* The PLL option allows for the usage of a wider frequency range and a more

|

||||

* stable clock with less jitter. This is why this option is default.

|

||||

*

|

||||

* The target frequency is computed from the PLL multiplier and the PLL divisor.

|

||||

* Use the following formula to compute your values:

|

||||

*

|

||||

* CORECLOCK = ((PLL_MUL + 1) * 1MHz) / PLL_DIV

|

||||

*

|

||||

* NOTE: The PLL circuit does not run with less than 32MHz while the maximum PLL

|

||||

* frequency is 96MHz. So PLL_MULL must be between 31 and 95!

|

||||

*

|

||||

*

|

||||

* The internal Oscillator used directly can lead to a slightly better power

|

||||

* efficiency to the cost of a less stable clock. Use this option when you know

|

||||

* what you are doing! The actual core frequency is adjusted as follows:

|

||||

*

|

||||

* CORECLOCK = 8MHz / DIV

|

||||

*

|

||||

* NOTE: A core clock frequency below 1MHz is not recommended

|

||||

*

|

||||

* @{

|

||||

*/

|

||||

#define CLOCK_USE_PLL (0)

|

||||

#define CLOCK_USE_XOSC32_DFLL (1)

|

||||

/*

|

||||

* 0: use XOSC32K (always 32.768kHz) to clock GCLK2

|

||||

* 1: use OSCULP32K factory calibrated (~32.768kHz) to clock GCLK2

|

||||

*

|

||||

* OSCULP32K is factory calibrated to be around 32.768kHz but this values can

|

||||

* be of by a couple off % points, so prefer XOSC32K as default configuration.

|

||||

*/

|

||||

#define GEN2_ULP32K (0)

|

||||

|

||||

#if CLOCK_USE_PLL

|

||||

/* edit these values to adjust the PLL output frequency */

|

||||

#define CLOCK_PLL_MUL (47U) /* must be >= 31 & <= 95 */

|

||||

#define CLOCK_PLL_DIV (1U) /* adjust to your needs */

|

||||

/* generate the actual used core clock frequency */

|

||||

#define CLOCK_CORECLOCK (((CLOCK_PLL_MUL + 1) * 1000000U) / CLOCK_PLL_DIV)

|

||||

#elif CLOCK_USE_XOSC32_DFLL

|

||||

/* Settings for 32 kHz external oscillator and 48 MHz DFLL */

|

||||

#define CLOCK_CORECLOCK (48000000U)

|

||||

#define CLOCK_XOSC32K (32768UL)

|

||||

#define CLOCK_8MHZ (1)

|

||||

#else

|

||||

/* edit this value to your needs */

|

||||

#define CLOCK_DIV (1U)

|

||||

/* generate the actual core clock frequency */

|

||||

#define CLOCK_CORECLOCK (8000000 / CLOCK_DIV)

|

||||

#endif

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name Timer peripheral configuration

|

||||

* @{

|

||||

*/

|

||||

static const tc32_conf_t timer_config[] = {

|

||||

{ /* Timer 0 - System Clock */

|

||||

.dev = TC0,

|

||||

.irq = TC0_IRQn,

|

||||

.pm_mask = PM_APBCMASK_TC0 | PM_APBCMASK_TC1,

|

||||

.gclk_ctrl = GCLK_CLKCTRL_ID_TC0_TC1,

|

||||

#if CLOCK_USE_PLL || CLOCK_USE_XOSC32_DFLL

|

||||

.gclk_src = SAM0_GCLK_1MHZ,

|

||||

#else

|

||||

.gclk_src = SAM0_GCLK_MAIN,

|

||||

#endif

|

||||

.flags = TC_CTRLA_MODE_COUNT32,

|

||||

},

|

||||

{ /* Timer 1 */

|

||||

.dev = TC4,

|

||||

.irq = TC4_IRQn,

|

||||

.pm_mask = PM_APBCMASK_TC4 | PM_APBCMASK_TC5,

|

||||

.gclk_ctrl = GCLK_CLKCTRL_ID_TC4_TC5,

|

||||

#if CLOCK_USE_PLL || CLOCK_USE_XOSC32_DFLL

|

||||

.gclk_src = SAM0_GCLK_1MHZ,

|

||||

#else

|

||||

.gclk_src = SAM0_GCLK_MAIN,

|

||||

#endif

|

||||

.flags = TC_CTRLA_MODE_COUNT32,

|

||||

}

|

||||

};

|

||||

|

||||

/* interrupt function name mapping */

|

||||

#define TIMER_0_ISR isr_tc0

|

||||

#define TIMER_1_ISR isr_tc4

|

||||

|

||||

#define TIMER_NUMOF ARRAY_SIZE(timer_config)

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name UART configuration

|

||||

* @{

|

||||

*/

|

||||

static const uart_conf_t uart_config[] = {

|

||||

{ /* Virtual COM Port */

|

||||

.dev = &SERCOM3->USART,

|

||||

.rx_pin = GPIO_PIN(PA,25),

|

||||

.tx_pin = GPIO_PIN(PA,24),

|

||||

#ifdef MODULE_PERIPH_UART_HW_FC

|

||||

.rts_pin = GPIO_UNDEF,

|

||||

.cts_pin = GPIO_UNDEF,

|

||||

#endif

|

||||

.mux = GPIO_MUX_C,

|

||||

.rx_pad = UART_PAD_RX_3,

|

||||

.tx_pad = UART_PAD_TX_2,

|

||||

.flags = UART_FLAG_NONE,

|

||||

.gclk_src = SAM0_GCLK_MAIN,

|

||||

},

|

||||

{ /* EXT1 */

|

||||

.dev = &SERCOM4->USART,

|

||||

.rx_pin = GPIO_PIN(PB,9),

|

||||

.tx_pin = GPIO_PIN(PB,8),

|

||||

#ifdef MODULE_PERIPH_UART_HW_FC

|

||||

.rts_pin = GPIO_UNDEF,

|

||||

.cts_pin = GPIO_UNDEF,

|

||||

#endif

|

||||

.mux = GPIO_MUX_D,

|

||||

.rx_pad = UART_PAD_RX_1,

|

||||

.tx_pad = UART_PAD_TX_0,

|

||||

.flags = UART_FLAG_NONE,

|

||||

.gclk_src = SAM0_GCLK_MAIN,

|

||||

},

|

||||

};

|

||||

|

||||

/* interrupt function name mapping */

|

||||

#define UART_0_ISR isr_sercom3

|

||||

#define UART_1_ISR isr_sercom4

|

||||

|

||||

#define UART_NUMOF ARRAY_SIZE(uart_config)

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name SPI configuration

|

||||

* @{

|

||||

*/

|

||||

static const spi_conf_t spi_config[] = {

|

||||

{ /* EXT1 */

|

||||

.dev = &SERCOM0->SPI,

|

||||

.miso_pin = GPIO_PIN(PA, 4),

|

||||

.mosi_pin = GPIO_PIN(PA, 6),

|

||||

.clk_pin = GPIO_PIN(PA, 7),

|

||||

.miso_mux = GPIO_MUX_D,

|

||||

.mosi_mux = GPIO_MUX_D,

|

||||

.clk_mux = GPIO_MUX_D,

|

||||

.miso_pad = SPI_PAD_MISO_0,

|

||||

.mosi_pad = SPI_PAD_MOSI_2_SCK_3,

|

||||

.gclk_src = SAM0_GCLK_MAIN,

|

||||

},

|

||||

{ /* EXT2 */

|

||||

.dev = &SERCOM1->SPI,

|

||||

.miso_pin = GPIO_PIN(PA, 16),

|

||||

.mosi_pin = GPIO_PIN(PA, 18),

|

||||

.clk_pin = GPIO_PIN(PA, 19),

|

||||

.miso_mux = GPIO_MUX_C,

|

||||

.mosi_mux = GPIO_MUX_C,

|

||||

.clk_mux = GPIO_MUX_C,

|

||||

.miso_pad = SPI_PAD_MISO_0,

|

||||

.mosi_pad = SPI_PAD_MOSI_2_SCK_3,

|

||||

.gclk_src = SAM0_GCLK_MAIN,

|

||||

},

|

||||

{ /* EXT3 */

|

||||

.dev = &SERCOM5->SPI,

|

||||

.miso_pin = GPIO_PIN(PB, 16),

|

||||

.mosi_pin = GPIO_PIN(PB, 22),

|

||||

.clk_pin = GPIO_PIN(PB, 23),

|

||||

.miso_mux = GPIO_MUX_C,

|

||||

.mosi_mux = GPIO_MUX_D,

|

||||

.clk_mux = GPIO_MUX_D,

|

||||

.miso_pad = SPI_PAD_MISO_0,

|

||||

.mosi_pad = SPI_PAD_MOSI_2_SCK_3,

|

||||

.gclk_src = SAM0_GCLK_MAIN,

|

||||

},

|

||||

};

|

||||

|

||||

#define SPI_NUMOF ARRAY_SIZE(spi_config)

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name I2C configuration

|

||||

* @{

|

||||

*/

|

||||

static const i2c_conf_t i2c_config[] = {

|

||||

{

|

||||

.dev = &(SERCOM2->I2CM),

|

||||

.speed = I2C_SPEED_NORMAL,

|

||||

.scl_pin = GPIO_PIN(PA, 9),

|

||||

.sda_pin = GPIO_PIN(PA, 8),

|

||||

.mux = GPIO_MUX_D,

|

||||

.gclk_src = SAM0_GCLK_MAIN,

|

||||

.flags = I2C_FLAG_NONE

|

||||

}

|

||||

};

|

||||

#define I2C_NUMOF ARRAY_SIZE(i2c_config)

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name RTT configuration

|

||||

* @{

|

||||

*/

|

||||

#ifndef RTT_FREQUENCY

|

||||

#define RTT_FREQUENCY (32768U) /* in Hz. For changes see `rtt.c` */

|

||||

#endif

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name PWM configuration

|

||||

* @{

|

||||

*/

|

||||

#define PWM_0_EN 1

|

||||

|

||||

#if PWM_0_EN

|

||||

/* PWM0 channels */

|

||||

static const pwm_conf_chan_t pwm_chan0_config[] = {

|

||||

/* GPIO pin, MUX value, TCC channel */

|

||||

{ GPIO_PIN(PA, 14), GPIO_MUX_E, 0 },

|

||||

};

|

||||

#endif

|

||||

|

||||

/* PWM device configuration */

|

||||

static const pwm_conf_t pwm_config[] = {

|

||||

#if PWM_0_EN

|

||||

{ .tim = TC_CONFIG(TC3),

|

||||

.chan = pwm_chan0_config,

|

||||

.chan_numof = ARRAY_SIZE(pwm_chan0_config),

|

||||

.gclk_src = SAM0_GCLK_1MHZ,

|

||||

},

|

||||

#endif

|

||||

};

|

||||

|

||||

/* number of devices that are actually defined */

|

||||

#define PWM_NUMOF ARRAY_SIZE(pwm_config)

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name ADC Configuration

|

||||

* @{

|

||||

*/

|

||||

|

||||

/* ADC Default values */

|

||||

#define ADC_PRESCALER ADC_CTRLB_PRESCALER_DIV128

|

||||

|

||||

#define ADC_NEG_INPUT ADC_INPUTCTRL_MUXNEG_GND

|

||||

#define ADC_GAIN_FACTOR_DEFAULT ADC_INPUTCTRL_GAIN_1X

|

||||

#define ADC_REF_DEFAULT ADC_REFCTRL_REFSEL_INT1V

|

||||

|

||||

static const adc_conf_chan_t adc_channels[] = {

|

||||

/* port, pin, muxpos */

|

||||

{GPIO_PIN(PB, 0), ADC_INPUTCTRL_MUXPOS_PIN8}, /* EXT1, pin 3 */

|

||||

{GPIO_PIN(PB, 1), ADC_INPUTCTRL_MUXPOS_PIN9}, /* EXT1, pin 4 */

|

||||

{GPIO_PIN(PA, 10), ADC_INPUTCTRL_MUXPOS_PIN18}, /* EXT2, pin 3 */

|

||||

{GPIO_PIN(PA, 11), ADC_INPUTCTRL_MUXPOS_PIN19}, /* EXT2, pin 4 */

|

||||

{GPIO_PIN(PA, 2), ADC_INPUTCTRL_MUXPOS_PIN0}, /* EXT3, pin 3 */

|

||||

{GPIO_PIN(PA, 3), ADC_INPUTCTRL_MUXPOS_PIN1} /* EXT3, pin 4.*/

|

||||

};

|

||||

|

||||

#define ADC_NUMOF ARRAY_SIZE(adc_channels)

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name DAC configuration

|

||||

* @{

|

||||

*/

|

||||

#define DAC_CLOCK SAM0_GCLK_1MHZ

|

||||

/* use Vcc as reference voltage */

|

||||

#define DAC_VREF DAC_CTRLB_REFSEL_AVCC

|

||||

/** @} */

|

||||

|

||||

#ifdef __cplusplus

|

||||

}

|

||||

#endif

|

||||

|

||||

#endif /* PERIPH_CONF_H */

|

||||

/** @} */

|

||||

@ -8,7 +8,6 @@

|

||||

config CPU_COMMON_SAM0

|

||||

bool

|

||||

select HAS_PERIPH_CPUID

|

||||

select HAS_PERIPH_DMA

|

||||

select HAS_PERIPH_FLASHPAGE

|

||||

select HAS_PERIPH_FLASHPAGE_PAGEWISE

|

||||

select HAS_PERIPH_FLASHPAGE_RWEE

|

||||

|

||||

@ -1,7 +1,12 @@

|

||||

CPU_FAM := $(shell echo $(CPU_MODEL) | cut -c -6)

|

||||

|

||||

FEATURES_PROVIDED += periph_cpuid

|

||||

FEATURES_PROVIDED += periph_dma

|

||||

|

||||

CPU_MODELS_WITHOUT_DMA = samd20%

|

||||

ifeq (,$(filter $(CPU_MODELS_WITHOUT_DMA),$(CPU_MODEL)))

|

||||

FEATURES_PROVIDED += periph_dma

|

||||

endif

|

||||

|

||||

FEATURES_PROVIDED += periph_flashpage

|

||||

FEATURES_PROVIDED += periph_flashpage_pagewise

|

||||

FEATURES_PROVIDED += periph_flashpage_rwee

|

||||

|

||||

@ -5,7 +5,7 @@ CFLAGS += -DCPU_FAM_$(call uppercase_and_underscore,$(CPU_FAM))

|

||||

CFLAGS += -D__$(call uppercase_and_underscore,$(CPU_MODEL))__

|

||||

|

||||

# Compute CPU_LINE

|

||||

LINE := $(shell echo $(CPU_MODEL) | sed -E -e 's/^sam([a-z][0-9][0-9])(.)([0-9][0-9])(.)/\1 \2 \3 \4/')

|

||||

LINE := $(shell echo $(CPU_MODEL) | sed -E -e 's/^sam([a-z][0-9][0-9])(.)([0-9][0-9])(.)*/\1 \2 \3 \4/')

|

||||

FAMILY := $(word 1, $(LINE))

|

||||

TYPE1 := $(word 2, $(LINE))

|

||||

MEMORY := $(word 3, $(LINE))

|

||||

@ -16,7 +16,7 @@ ROM_LEN := $(shell echo $$((1 << $(MEMORY))))

|

||||

|

||||

# get vendor file to extract RAM length

|

||||

VENDOR_FILE := $(shell find $(RIOTCPU)/sam0_common/include/vendor/sam$(FAMILY) -name $(CPU_MODEL).h | grep include.*/sam)

|

||||

RAM_LEN := $(shell sed -E -n 's/\#define (HMCRAMC0_SIZE|HSRAM_SIZE).*(0x[[:xdigit:]]*).*/\2/p' $(VENDOR_FILE))

|

||||

RAM_LEN := $(shell sed -E -n 's/\#define (HRAMC0_SIZE|HMCRAMC0_SIZE|HSRAM_SIZE).*(0x[[:xdigit:]]*).*/\2/p' $(VENDOR_FILE))

|

||||

|

||||

ROM_START_ADDR ?= 0x00000000

|

||||

RAM_START_ADDR ?= 0x20000000

|

||||

|

||||

@ -31,6 +31,10 @@

|

||||

|

||||

#if defined(CPU_SAMD10)

|

||||

#include "vendor/samd10/include/samd10.h"

|

||||

#elif defined(CPU_SAMD20)

|

||||

#include "vendor/samd20/include/samd20.h"

|

||||

#elif defined(CPU_SAMD20B)

|

||||

#include "vendor/samd20/include_b/samd20.h"

|

||||

#elif defined(CPU_SAMD21A)

|

||||

#include "vendor/samd21/include_a/samd21.h"

|

||||

#elif defined(CPU_SAMD21B)

|

||||

|

||||

@ -849,6 +849,7 @@ typedef struct {

|

||||

*/

|

||||

#define WDT_HAS_INIT (1)

|

||||

|

||||

#if defined(REV_DMAC) || DOXYGEN

|

||||

/**

|

||||

* @name sam0 DMA peripheral

|

||||

* @{

|

||||

@ -1117,6 +1118,7 @@ void dma_wait(dma_t dma);

|

||||

*/

|

||||

void dma_cancel(dma_t dma);

|

||||

/** @} */

|

||||

#endif /* REV_DMAC || DOXYGEN */

|

||||

|

||||

/**

|

||||

* @name sam0 RTC Tamper Detection

|

||||

|

||||

4

cpu/sam0_common/include/vendor/README.md

vendored

4

cpu/sam0_common/include/vendor/README.md

vendored

@ -45,6 +45,10 @@ resolve any CPU family specific includes required.

|

||||

|

||||

samd10: `Atmel.SAMD10_DFP.1.1.77.atpack`

|

||||

|

||||

## SAMD20 files

|

||||

|

||||

samd20: `Atmel.SAMD20_DFP.1.3.165.atpack`

|

||||

|

||||

Each atpack has an include subdirectory with the files we copy into

|

||||

RIOT. The files are copied unmodified.

|

||||

|

||||

|

||||

64

cpu/sam0_common/include/vendor/samd20/include/component-version.h

vendored

Normal file

64

cpu/sam0_common/include/vendor/samd20/include/component-version.h

vendored

Normal file

@ -0,0 +1,64 @@

|

||||

/**

|

||||

* \file

|

||||

*

|

||||

* \brief Component version header file

|

||||

*

|

||||

* Copyright (c) 2020 Atmel Corporation, a wholly owned subsidiary of Microchip Technology Inc.

|

||||

*

|

||||

* \license_start

|

||||

*

|

||||

* \page License

|

||||

*

|

||||

* Licensed under the Apache License, Version 2.0 (the "License");

|

||||

* you may not use this file except in compliance with the License.

|

||||

* You may obtain a copy of the License at

|

||||

*

|

||||

* http://www.apache.org/licenses/LICENSE-2.0

|

||||

*

|

||||

* Unless required by applicable law or agreed to in writing, software

|

||||

* distributed under the License is distributed on an "AS IS" BASIS,

|

||||

* WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

|

||||

* See the License for the specific language governing permissions and

|

||||

* limitations under the License.

|

||||

*

|

||||

* \license_stop

|

||||

*

|

||||

*/

|

||||

|

||||

#ifndef _COMPONENT_VERSION_H_INCLUDED

|

||||

#define _COMPONENT_VERSION_H_INCLUDED

|

||||

|

||||

#define COMPONENT_VERSION_MAJOR 1

|

||||

#define COMPONENT_VERSION_MINOR 3

|

||||

|

||||

//

|

||||

// The COMPONENT_VERSION define is composed of the major and the minor version number.

|

||||

//

|

||||

// The last four digits of the COMPONENT_VERSION is the minor version with leading zeros.

|

||||

// The rest of the COMPONENT_VERSION is the major version.

|

||||

//

|

||||

#define COMPONENT_VERSION 10003

|

||||

|

||||

//

|

||||

// The build number does not refer to the component, but to the build number

|

||||

// of the device pack that provides the component.

|

||||

//

|

||||

#define BUILD_NUMBER 165

|

||||

|

||||

//

|

||||

// The COMPONENT_VERSION_STRING is a string (enclosed in ") that can be used for logging or embedding.

|

||||

//

|

||||

#define COMPONENT_VERSION_STRING "1.3"

|

||||

|

||||

//

|

||||

// The COMPONENT_DATE_STRING contains a timestamp of when the pack was generated.

|

||||

//

|

||||

// The COMPONENT_DATE_STRING is written out using the following strftime pattern.

|

||||

//

|

||||

// "%Y-%m-%d %H:%M:%S"

|

||||

//

|

||||

//

|

||||

#define COMPONENT_DATE_STRING "2020-01-20 13:50:55"

|

||||

|

||||

#endif/* #ifndef _COMPONENT_VERSION_H_INCLUDED */

|

||||

|

||||

545

cpu/sam0_common/include/vendor/samd20/include/component/ac.h

vendored

Normal file

545

cpu/sam0_common/include/vendor/samd20/include/component/ac.h

vendored

Normal file

@ -0,0 +1,545 @@

|

||||

/**

|

||||

* \file

|

||||

*

|

||||

* \brief Component description for AC

|

||||

*

|

||||

* Copyright (c) 2018 Microchip Technology Inc.

|

||||

*

|

||||

* \asf_license_start

|

||||

*

|

||||

* \page License

|

||||

*

|

||||

* SPDX-License-Identifier: Apache-2.0

|

||||

*

|

||||

* Licensed under the Apache License, Version 2.0 (the "License"); you may

|

||||

* not use this file except in compliance with the License.

|

||||

* You may obtain a copy of the Licence at

|

||||

*

|

||||

* http://www.apache.org/licenses/LICENSE-2.0

|

||||

*

|

||||

* Unless required by applicable law or agreed to in writing, software

|

||||

* distributed under the License is distributed on an AS IS BASIS, WITHOUT

|

||||

* WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied.

|

||||

* See the License for the specific language governing permissions and

|

||||

* limitations under the License.

|

||||

*

|

||||

* \asf_license_stop

|

||||

*

|

||||

*/

|

||||

|

||||

#ifndef _SAMD20_AC_COMPONENT_

|

||||

#define _SAMD20_AC_COMPONENT_

|

||||

|

||||

/* ========================================================================== */

|

||||

/** SOFTWARE API DEFINITION FOR AC */

|

||||

/* ========================================================================== */

|

||||

/** \addtogroup SAMD20_AC Analog Comparators */

|

||||

/*@{*/

|

||||

|

||||

#define AC_U2205

|

||||

#define REV_AC 0x111

|

||||

|

||||

/* -------- AC_CTRLA : (AC Offset: 0x00) (R/W 8) Control A -------- */

|

||||

#if !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__))

|

||||

typedef union {

|

||||

struct {

|

||||

uint8_t SWRST:1; /*!< bit: 0 Software Reset */

|

||||

uint8_t ENABLE:1; /*!< bit: 1 Enable */

|

||||

uint8_t RUNSTDBY:1; /*!< bit: 2 Run in Standby */

|

||||

uint8_t :4; /*!< bit: 3.. 6 Reserved */

|

||||

uint8_t LPMUX:1; /*!< bit: 7 Low-Power Mux */

|

||||

} bit; /*!< Structure used for bit access */

|

||||

uint8_t reg; /*!< Type used for register access */

|

||||

} AC_CTRLA_Type;

|

||||

#endif /* !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__)) */

|

||||

|

||||

#define AC_CTRLA_OFFSET 0x00 /**< \brief (AC_CTRLA offset) Control A */

|

||||

#define AC_CTRLA_RESETVALUE _U_(0x00) /**< \brief (AC_CTRLA reset_value) Control A */

|

||||

|

||||

#define AC_CTRLA_SWRST_Pos 0 /**< \brief (AC_CTRLA) Software Reset */

|

||||

#define AC_CTRLA_SWRST (_U_(0x1) << AC_CTRLA_SWRST_Pos)

|

||||

#define AC_CTRLA_ENABLE_Pos 1 /**< \brief (AC_CTRLA) Enable */

|

||||

#define AC_CTRLA_ENABLE (_U_(0x1) << AC_CTRLA_ENABLE_Pos)

|

||||

#define AC_CTRLA_RUNSTDBY_Pos 2 /**< \brief (AC_CTRLA) Run in Standby */

|

||||

#define AC_CTRLA_RUNSTDBY_Msk (_U_(0x1) << AC_CTRLA_RUNSTDBY_Pos)

|

||||

#define AC_CTRLA_RUNSTDBY(value) (AC_CTRLA_RUNSTDBY_Msk & ((value) << AC_CTRLA_RUNSTDBY_Pos))

|

||||

#define AC_CTRLA_LPMUX_Pos 7 /**< \brief (AC_CTRLA) Low-Power Mux */

|

||||

#define AC_CTRLA_LPMUX (_U_(0x1) << AC_CTRLA_LPMUX_Pos)

|

||||

#define AC_CTRLA_MASK _U_(0x87) /**< \brief (AC_CTRLA) MASK Register */

|

||||

|

||||

/* -------- AC_CTRLB : (AC Offset: 0x01) ( /W 8) Control B -------- */

|

||||

#if !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__))

|

||||

typedef union {

|

||||

struct {

|

||||

uint8_t START0:1; /*!< bit: 0 Comparator 0 Start Comparison */

|

||||

uint8_t START1:1; /*!< bit: 1 Comparator 1 Start Comparison */

|

||||

uint8_t :6; /*!< bit: 2.. 7 Reserved */

|

||||

} bit; /*!< Structure used for bit access */

|

||||

struct {

|

||||

uint8_t START:2; /*!< bit: 0.. 1 Comparator x Start Comparison */

|

||||

uint8_t :6; /*!< bit: 2.. 7 Reserved */

|

||||

} vec; /*!< Structure used for vec access */

|

||||

uint8_t reg; /*!< Type used for register access */

|

||||

} AC_CTRLB_Type;

|

||||

#endif /* !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__)) */

|

||||

|

||||

#define AC_CTRLB_OFFSET 0x01 /**< \brief (AC_CTRLB offset) Control B */

|

||||

#define AC_CTRLB_RESETVALUE _U_(0x00) /**< \brief (AC_CTRLB reset_value) Control B */

|

||||

|

||||

#define AC_CTRLB_START0_Pos 0 /**< \brief (AC_CTRLB) Comparator 0 Start Comparison */

|

||||

#define AC_CTRLB_START0 (_U_(1) << AC_CTRLB_START0_Pos)

|

||||

#define AC_CTRLB_START1_Pos 1 /**< \brief (AC_CTRLB) Comparator 1 Start Comparison */

|

||||

#define AC_CTRLB_START1 (_U_(1) << AC_CTRLB_START1_Pos)

|

||||

#define AC_CTRLB_START_Pos 0 /**< \brief (AC_CTRLB) Comparator x Start Comparison */

|

||||

#define AC_CTRLB_START_Msk (_U_(0x3) << AC_CTRLB_START_Pos)

|

||||

#define AC_CTRLB_START(value) (AC_CTRLB_START_Msk & ((value) << AC_CTRLB_START_Pos))

|

||||

#define AC_CTRLB_MASK _U_(0x03) /**< \brief (AC_CTRLB) MASK Register */

|

||||

|

||||

/* -------- AC_EVCTRL : (AC Offset: 0x02) (R/W 16) Event Control -------- */

|

||||

#if !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__))

|

||||

typedef union {

|

||||

struct {

|

||||

uint16_t COMPEO0:1; /*!< bit: 0 Comparator 0 Event Output Enable */

|

||||

uint16_t COMPEO1:1; /*!< bit: 1 Comparator 1 Event Output Enable */

|

||||

uint16_t :2; /*!< bit: 2.. 3 Reserved */

|

||||

uint16_t WINEO0:1; /*!< bit: 4 Window 0 Event Output Enable */

|

||||

uint16_t :3; /*!< bit: 5.. 7 Reserved */

|

||||

uint16_t COMPEI0:1; /*!< bit: 8 Comparator 0 Event Input */

|

||||

uint16_t COMPEI1:1; /*!< bit: 9 Comparator 1 Event Input */

|

||||

uint16_t :6; /*!< bit: 10..15 Reserved */

|

||||

} bit; /*!< Structure used for bit access */

|

||||

struct {

|

||||

uint16_t COMPEO:2; /*!< bit: 0.. 1 Comparator x Event Output Enable */

|

||||

uint16_t :2; /*!< bit: 2.. 3 Reserved */

|

||||

uint16_t WINEO:1; /*!< bit: 4 Window x Event Output Enable */

|

||||

uint16_t :3; /*!< bit: 5.. 7 Reserved */

|

||||

uint16_t COMPEI:2; /*!< bit: 8.. 9 Comparator x Event Input */

|

||||

uint16_t :6; /*!< bit: 10..15 Reserved */

|

||||

} vec; /*!< Structure used for vec access */

|

||||

uint16_t reg; /*!< Type used for register access */

|

||||

} AC_EVCTRL_Type;

|

||||

#endif /* !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__)) */

|

||||

|

||||

#define AC_EVCTRL_OFFSET 0x02 /**< \brief (AC_EVCTRL offset) Event Control */

|

||||

#define AC_EVCTRL_RESETVALUE _U_(0x0000) /**< \brief (AC_EVCTRL reset_value) Event Control */

|

||||

|

||||

#define AC_EVCTRL_COMPEO0_Pos 0 /**< \brief (AC_EVCTRL) Comparator 0 Event Output Enable */

|

||||

#define AC_EVCTRL_COMPEO0 (_U_(1) << AC_EVCTRL_COMPEO0_Pos)

|

||||

#define AC_EVCTRL_COMPEO1_Pos 1 /**< \brief (AC_EVCTRL) Comparator 1 Event Output Enable */

|

||||

#define AC_EVCTRL_COMPEO1 (_U_(1) << AC_EVCTRL_COMPEO1_Pos)

|

||||

#define AC_EVCTRL_COMPEO_Pos 0 /**< \brief (AC_EVCTRL) Comparator x Event Output Enable */

|

||||

#define AC_EVCTRL_COMPEO_Msk (_U_(0x3) << AC_EVCTRL_COMPEO_Pos)

|

||||

#define AC_EVCTRL_COMPEO(value) (AC_EVCTRL_COMPEO_Msk & ((value) << AC_EVCTRL_COMPEO_Pos))

|

||||

#define AC_EVCTRL_WINEO0_Pos 4 /**< \brief (AC_EVCTRL) Window 0 Event Output Enable */

|

||||

#define AC_EVCTRL_WINEO0 (_U_(1) << AC_EVCTRL_WINEO0_Pos)

|

||||

#define AC_EVCTRL_WINEO_Pos 4 /**< \brief (AC_EVCTRL) Window x Event Output Enable */

|

||||

#define AC_EVCTRL_WINEO_Msk (_U_(0x1) << AC_EVCTRL_WINEO_Pos)

|

||||

#define AC_EVCTRL_WINEO(value) (AC_EVCTRL_WINEO_Msk & ((value) << AC_EVCTRL_WINEO_Pos))

|

||||

#define AC_EVCTRL_COMPEI0_Pos 8 /**< \brief (AC_EVCTRL) Comparator 0 Event Input */

|

||||

#define AC_EVCTRL_COMPEI0 (_U_(1) << AC_EVCTRL_COMPEI0_Pos)

|

||||

#define AC_EVCTRL_COMPEI1_Pos 9 /**< \brief (AC_EVCTRL) Comparator 1 Event Input */

|

||||

#define AC_EVCTRL_COMPEI1 (_U_(1) << AC_EVCTRL_COMPEI1_Pos)

|

||||

#define AC_EVCTRL_COMPEI_Pos 8 /**< \brief (AC_EVCTRL) Comparator x Event Input */

|

||||

#define AC_EVCTRL_COMPEI_Msk (_U_(0x3) << AC_EVCTRL_COMPEI_Pos)

|

||||

#define AC_EVCTRL_COMPEI(value) (AC_EVCTRL_COMPEI_Msk & ((value) << AC_EVCTRL_COMPEI_Pos))

|

||||

#define AC_EVCTRL_MASK _U_(0x0313) /**< \brief (AC_EVCTRL) MASK Register */

|

||||

|

||||

/* -------- AC_INTENCLR : (AC Offset: 0x04) (R/W 8) Interrupt Enable Clear -------- */

|

||||

#if !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__))

|

||||

typedef union {

|

||||

struct {

|

||||

uint8_t COMP0:1; /*!< bit: 0 Comparator 0 Interrupt Enable */

|

||||

uint8_t COMP1:1; /*!< bit: 1 Comparator 1 Interrupt Enable */

|

||||

uint8_t :2; /*!< bit: 2.. 3 Reserved */

|

||||

uint8_t WIN0:1; /*!< bit: 4 Window 0 Interrupt Enable */

|

||||

uint8_t :3; /*!< bit: 5.. 7 Reserved */

|

||||

} bit; /*!< Structure used for bit access */

|

||||

struct {

|

||||

uint8_t COMP:2; /*!< bit: 0.. 1 Comparator x Interrupt Enable */

|

||||

uint8_t :2; /*!< bit: 2.. 3 Reserved */

|

||||

uint8_t WIN:1; /*!< bit: 4 Window x Interrupt Enable */

|

||||

uint8_t :3; /*!< bit: 5.. 7 Reserved */

|

||||

} vec; /*!< Structure used for vec access */

|

||||

uint8_t reg; /*!< Type used for register access */

|

||||

} AC_INTENCLR_Type;

|

||||

#endif /* !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__)) */

|

||||

|

||||

#define AC_INTENCLR_OFFSET 0x04 /**< \brief (AC_INTENCLR offset) Interrupt Enable Clear */

|

||||

#define AC_INTENCLR_RESETVALUE _U_(0x00) /**< \brief (AC_INTENCLR reset_value) Interrupt Enable Clear */

|

||||

|

||||

#define AC_INTENCLR_COMP0_Pos 0 /**< \brief (AC_INTENCLR) Comparator 0 Interrupt Enable */

|

||||

#define AC_INTENCLR_COMP0 (_U_(1) << AC_INTENCLR_COMP0_Pos)

|

||||

#define AC_INTENCLR_COMP1_Pos 1 /**< \brief (AC_INTENCLR) Comparator 1 Interrupt Enable */

|

||||

#define AC_INTENCLR_COMP1 (_U_(1) << AC_INTENCLR_COMP1_Pos)

|

||||

#define AC_INTENCLR_COMP_Pos 0 /**< \brief (AC_INTENCLR) Comparator x Interrupt Enable */

|

||||

#define AC_INTENCLR_COMP_Msk (_U_(0x3) << AC_INTENCLR_COMP_Pos)

|

||||

#define AC_INTENCLR_COMP(value) (AC_INTENCLR_COMP_Msk & ((value) << AC_INTENCLR_COMP_Pos))

|

||||

#define AC_INTENCLR_WIN0_Pos 4 /**< \brief (AC_INTENCLR) Window 0 Interrupt Enable */

|

||||

#define AC_INTENCLR_WIN0 (_U_(1) << AC_INTENCLR_WIN0_Pos)

|

||||

#define AC_INTENCLR_WIN_Pos 4 /**< \brief (AC_INTENCLR) Window x Interrupt Enable */

|

||||

#define AC_INTENCLR_WIN_Msk (_U_(0x1) << AC_INTENCLR_WIN_Pos)

|

||||

#define AC_INTENCLR_WIN(value) (AC_INTENCLR_WIN_Msk & ((value) << AC_INTENCLR_WIN_Pos))

|

||||

#define AC_INTENCLR_MASK _U_(0x13) /**< \brief (AC_INTENCLR) MASK Register */

|

||||

|

||||

/* -------- AC_INTENSET : (AC Offset: 0x05) (R/W 8) Interrupt Enable Set -------- */

|

||||

#if !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__))

|

||||

typedef union {

|

||||

struct {

|

||||

uint8_t COMP0:1; /*!< bit: 0 Comparator 0 Interrupt Enable */

|

||||

uint8_t COMP1:1; /*!< bit: 1 Comparator 1 Interrupt Enable */

|

||||

uint8_t :2; /*!< bit: 2.. 3 Reserved */

|

||||

uint8_t WIN0:1; /*!< bit: 4 Window 0 Interrupt Enable */

|

||||

uint8_t :3; /*!< bit: 5.. 7 Reserved */

|

||||

} bit; /*!< Structure used for bit access */

|

||||

struct {

|

||||

uint8_t COMP:2; /*!< bit: 0.. 1 Comparator x Interrupt Enable */

|

||||

uint8_t :2; /*!< bit: 2.. 3 Reserved */

|

||||

uint8_t WIN:1; /*!< bit: 4 Window x Interrupt Enable */

|

||||

uint8_t :3; /*!< bit: 5.. 7 Reserved */

|

||||

} vec; /*!< Structure used for vec access */

|

||||

uint8_t reg; /*!< Type used for register access */

|

||||

} AC_INTENSET_Type;

|

||||

#endif /* !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__)) */

|

||||

|

||||

#define AC_INTENSET_OFFSET 0x05 /**< \brief (AC_INTENSET offset) Interrupt Enable Set */

|

||||

#define AC_INTENSET_RESETVALUE _U_(0x00) /**< \brief (AC_INTENSET reset_value) Interrupt Enable Set */

|

||||

|

||||

#define AC_INTENSET_COMP0_Pos 0 /**< \brief (AC_INTENSET) Comparator 0 Interrupt Enable */

|

||||

#define AC_INTENSET_COMP0 (_U_(1) << AC_INTENSET_COMP0_Pos)

|

||||

#define AC_INTENSET_COMP1_Pos 1 /**< \brief (AC_INTENSET) Comparator 1 Interrupt Enable */

|

||||

#define AC_INTENSET_COMP1 (_U_(1) << AC_INTENSET_COMP1_Pos)

|

||||

#define AC_INTENSET_COMP_Pos 0 /**< \brief (AC_INTENSET) Comparator x Interrupt Enable */

|

||||

#define AC_INTENSET_COMP_Msk (_U_(0x3) << AC_INTENSET_COMP_Pos)

|

||||

#define AC_INTENSET_COMP(value) (AC_INTENSET_COMP_Msk & ((value) << AC_INTENSET_COMP_Pos))

|

||||

#define AC_INTENSET_WIN0_Pos 4 /**< \brief (AC_INTENSET) Window 0 Interrupt Enable */

|

||||

#define AC_INTENSET_WIN0 (_U_(1) << AC_INTENSET_WIN0_Pos)

|

||||

#define AC_INTENSET_WIN_Pos 4 /**< \brief (AC_INTENSET) Window x Interrupt Enable */

|

||||

#define AC_INTENSET_WIN_Msk (_U_(0x1) << AC_INTENSET_WIN_Pos)

|

||||

#define AC_INTENSET_WIN(value) (AC_INTENSET_WIN_Msk & ((value) << AC_INTENSET_WIN_Pos))

|

||||

#define AC_INTENSET_MASK _U_(0x13) /**< \brief (AC_INTENSET) MASK Register */

|

||||

|

||||

/* -------- AC_INTFLAG : (AC Offset: 0x06) (R/W 8) Interrupt Flag Status and Clear -------- */

|

||||

#if !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__))

|

||||

typedef union { // __I to avoid read-modify-write on write-to-clear register

|

||||

struct {

|

||||

__I uint8_t COMP0:1; /*!< bit: 0 Comparator 0 */

|

||||

__I uint8_t COMP1:1; /*!< bit: 1 Comparator 1 */

|

||||

__I uint8_t :2; /*!< bit: 2.. 3 Reserved */

|

||||

__I uint8_t WIN0:1; /*!< bit: 4 Window 0 */

|

||||

__I uint8_t :3; /*!< bit: 5.. 7 Reserved */

|

||||

} bit; /*!< Structure used for bit access */

|

||||

struct {

|

||||

__I uint8_t COMP:2; /*!< bit: 0.. 1 Comparator x */

|

||||

__I uint8_t :2; /*!< bit: 2.. 3 Reserved */

|

||||

__I uint8_t WIN:1; /*!< bit: 4 Window x */

|

||||

__I uint8_t :3; /*!< bit: 5.. 7 Reserved */

|

||||

} vec; /*!< Structure used for vec access */

|

||||

uint8_t reg; /*!< Type used for register access */

|

||||

} AC_INTFLAG_Type;

|

||||

#endif /* !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__)) */

|

||||

|

||||

#define AC_INTFLAG_OFFSET 0x06 /**< \brief (AC_INTFLAG offset) Interrupt Flag Status and Clear */

|

||||

#define AC_INTFLAG_RESETVALUE _U_(0x00) /**< \brief (AC_INTFLAG reset_value) Interrupt Flag Status and Clear */

|

||||

|

||||

#define AC_INTFLAG_COMP0_Pos 0 /**< \brief (AC_INTFLAG) Comparator 0 */

|

||||

#define AC_INTFLAG_COMP0 (_U_(1) << AC_INTFLAG_COMP0_Pos)

|

||||

#define AC_INTFLAG_COMP1_Pos 1 /**< \brief (AC_INTFLAG) Comparator 1 */

|

||||

#define AC_INTFLAG_COMP1 (_U_(1) << AC_INTFLAG_COMP1_Pos)

|

||||

#define AC_INTFLAG_COMP_Pos 0 /**< \brief (AC_INTFLAG) Comparator x */

|

||||

#define AC_INTFLAG_COMP_Msk (_U_(0x3) << AC_INTFLAG_COMP_Pos)

|

||||

#define AC_INTFLAG_COMP(value) (AC_INTFLAG_COMP_Msk & ((value) << AC_INTFLAG_COMP_Pos))

|

||||

#define AC_INTFLAG_WIN0_Pos 4 /**< \brief (AC_INTFLAG) Window 0 */

|

||||

#define AC_INTFLAG_WIN0 (_U_(1) << AC_INTFLAG_WIN0_Pos)

|

||||

#define AC_INTFLAG_WIN_Pos 4 /**< \brief (AC_INTFLAG) Window x */

|

||||

#define AC_INTFLAG_WIN_Msk (_U_(0x1) << AC_INTFLAG_WIN_Pos)

|

||||

#define AC_INTFLAG_WIN(value) (AC_INTFLAG_WIN_Msk & ((value) << AC_INTFLAG_WIN_Pos))

|

||||

#define AC_INTFLAG_MASK _U_(0x13) /**< \brief (AC_INTFLAG) MASK Register */

|

||||

|

||||

/* -------- AC_STATUSA : (AC Offset: 0x08) (R/ 8) Status A -------- */

|

||||

#if !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__))

|

||||

typedef union {

|

||||

struct {

|

||||

uint8_t STATE0:1; /*!< bit: 0 Comparator 0 Current State */

|

||||

uint8_t STATE1:1; /*!< bit: 1 Comparator 1 Current State */

|

||||

uint8_t :2; /*!< bit: 2.. 3 Reserved */

|

||||

uint8_t WSTATE0:2; /*!< bit: 4.. 5 Window 0 Current State */

|

||||

uint8_t :2; /*!< bit: 6.. 7 Reserved */

|

||||

} bit; /*!< Structure used for bit access */

|

||||

struct {

|

||||

uint8_t STATE:2; /*!< bit: 0.. 1 Comparator x Current State */

|

||||

uint8_t :6; /*!< bit: 2.. 7 Reserved */

|

||||

} vec; /*!< Structure used for vec access */

|

||||

uint8_t reg; /*!< Type used for register access */

|

||||

} AC_STATUSA_Type;

|

||||

#endif /* !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__)) */

|

||||

|

||||

#define AC_STATUSA_OFFSET 0x08 /**< \brief (AC_STATUSA offset) Status A */

|

||||

#define AC_STATUSA_RESETVALUE _U_(0x00) /**< \brief (AC_STATUSA reset_value) Status A */

|

||||

|

||||

#define AC_STATUSA_STATE0_Pos 0 /**< \brief (AC_STATUSA) Comparator 0 Current State */

|

||||

#define AC_STATUSA_STATE0 (_U_(1) << AC_STATUSA_STATE0_Pos)

|

||||

#define AC_STATUSA_STATE1_Pos 1 /**< \brief (AC_STATUSA) Comparator 1 Current State */

|

||||

#define AC_STATUSA_STATE1 (_U_(1) << AC_STATUSA_STATE1_Pos)

|

||||

#define AC_STATUSA_STATE_Pos 0 /**< \brief (AC_STATUSA) Comparator x Current State */

|

||||

#define AC_STATUSA_STATE_Msk (_U_(0x3) << AC_STATUSA_STATE_Pos)

|

||||

#define AC_STATUSA_STATE(value) (AC_STATUSA_STATE_Msk & ((value) << AC_STATUSA_STATE_Pos))

|

||||

#define AC_STATUSA_WSTATE0_Pos 4 /**< \brief (AC_STATUSA) Window 0 Current State */

|

||||

#define AC_STATUSA_WSTATE0_Msk (_U_(0x3) << AC_STATUSA_WSTATE0_Pos)

|

||||

#define AC_STATUSA_WSTATE0(value) (AC_STATUSA_WSTATE0_Msk & ((value) << AC_STATUSA_WSTATE0_Pos))

|

||||

#define AC_STATUSA_WSTATE0_ABOVE_Val _U_(0x0) /**< \brief (AC_STATUSA) Signal is above window */

|

||||

#define AC_STATUSA_WSTATE0_INSIDE_Val _U_(0x1) /**< \brief (AC_STATUSA) Signal is inside window */

|

||||

#define AC_STATUSA_WSTATE0_BELOW_Val _U_(0x2) /**< \brief (AC_STATUSA) Signal is below window */

|

||||

#define AC_STATUSA_WSTATE0_ABOVE (AC_STATUSA_WSTATE0_ABOVE_Val << AC_STATUSA_WSTATE0_Pos)

|

||||

#define AC_STATUSA_WSTATE0_INSIDE (AC_STATUSA_WSTATE0_INSIDE_Val << AC_STATUSA_WSTATE0_Pos)

|

||||

#define AC_STATUSA_WSTATE0_BELOW (AC_STATUSA_WSTATE0_BELOW_Val << AC_STATUSA_WSTATE0_Pos)

|

||||

#define AC_STATUSA_MASK _U_(0x33) /**< \brief (AC_STATUSA) MASK Register */

|

||||

|

||||

/* -------- AC_STATUSB : (AC Offset: 0x09) (R/ 8) Status B -------- */

|

||||

#if !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__))

|

||||

typedef union {

|

||||

struct {

|

||||

uint8_t READY0:1; /*!< bit: 0 Comparator 0 Ready */

|

||||

uint8_t READY1:1; /*!< bit: 1 Comparator 1 Ready */

|

||||

uint8_t :5; /*!< bit: 2.. 6 Reserved */

|

||||

uint8_t SYNCBUSY:1; /*!< bit: 7 Synchronization Busy */

|

||||

} bit; /*!< Structure used for bit access */

|

||||

struct {

|

||||

uint8_t READY:2; /*!< bit: 0.. 1 Comparator x Ready */

|

||||

uint8_t :6; /*!< bit: 2.. 7 Reserved */

|

||||

} vec; /*!< Structure used for vec access */

|

||||

uint8_t reg; /*!< Type used for register access */

|

||||

} AC_STATUSB_Type;

|

||||

#endif /* !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__)) */

|

||||

|

||||

#define AC_STATUSB_OFFSET 0x09 /**< \brief (AC_STATUSB offset) Status B */

|

||||

#define AC_STATUSB_RESETVALUE _U_(0x00) /**< \brief (AC_STATUSB reset_value) Status B */

|

||||

|

||||

#define AC_STATUSB_READY0_Pos 0 /**< \brief (AC_STATUSB) Comparator 0 Ready */

|

||||

#define AC_STATUSB_READY0 (_U_(1) << AC_STATUSB_READY0_Pos)

|

||||

#define AC_STATUSB_READY1_Pos 1 /**< \brief (AC_STATUSB) Comparator 1 Ready */

|

||||

#define AC_STATUSB_READY1 (_U_(1) << AC_STATUSB_READY1_Pos)

|

||||

#define AC_STATUSB_READY_Pos 0 /**< \brief (AC_STATUSB) Comparator x Ready */

|

||||

#define AC_STATUSB_READY_Msk (_U_(0x3) << AC_STATUSB_READY_Pos)

|

||||

#define AC_STATUSB_READY(value) (AC_STATUSB_READY_Msk & ((value) << AC_STATUSB_READY_Pos))

|

||||

#define AC_STATUSB_SYNCBUSY_Pos 7 /**< \brief (AC_STATUSB) Synchronization Busy */

|

||||

#define AC_STATUSB_SYNCBUSY (_U_(0x1) << AC_STATUSB_SYNCBUSY_Pos)

|

||||

#define AC_STATUSB_MASK _U_(0x83) /**< \brief (AC_STATUSB) MASK Register */

|

||||

|

||||

/* -------- AC_STATUSC : (AC Offset: 0x0A) (R/ 8) Status C -------- */

|

||||

#if !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__))

|

||||

typedef union {

|

||||

struct {

|

||||

uint8_t STATE0:1; /*!< bit: 0 Comparator 0 Current State */

|

||||

uint8_t STATE1:1; /*!< bit: 1 Comparator 1 Current State */

|

||||

uint8_t :2; /*!< bit: 2.. 3 Reserved */

|

||||

uint8_t WSTATE0:2; /*!< bit: 4.. 5 Window 0 Current State */

|

||||

uint8_t :2; /*!< bit: 6.. 7 Reserved */

|

||||

} bit; /*!< Structure used for bit access */

|

||||

struct {

|

||||

uint8_t STATE:2; /*!< bit: 0.. 1 Comparator x Current State */

|

||||

uint8_t :6; /*!< bit: 2.. 7 Reserved */

|

||||

} vec; /*!< Structure used for vec access */

|

||||

uint8_t reg; /*!< Type used for register access */

|

||||

} AC_STATUSC_Type;

|

||||

#endif /* !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__)) */

|

||||

|

||||

#define AC_STATUSC_OFFSET 0x0A /**< \brief (AC_STATUSC offset) Status C */

|

||||

#define AC_STATUSC_RESETVALUE _U_(0x00) /**< \brief (AC_STATUSC reset_value) Status C */

|

||||

|

||||

#define AC_STATUSC_STATE0_Pos 0 /**< \brief (AC_STATUSC) Comparator 0 Current State */

|

||||

#define AC_STATUSC_STATE0 (_U_(1) << AC_STATUSC_STATE0_Pos)

|

||||

#define AC_STATUSC_STATE1_Pos 1 /**< \brief (AC_STATUSC) Comparator 1 Current State */

|

||||

#define AC_STATUSC_STATE1 (_U_(1) << AC_STATUSC_STATE1_Pos)

|

||||

#define AC_STATUSC_STATE_Pos 0 /**< \brief (AC_STATUSC) Comparator x Current State */

|

||||

#define AC_STATUSC_STATE_Msk (_U_(0x3) << AC_STATUSC_STATE_Pos)

|

||||

#define AC_STATUSC_STATE(value) (AC_STATUSC_STATE_Msk & ((value) << AC_STATUSC_STATE_Pos))

|

||||

#define AC_STATUSC_WSTATE0_Pos 4 /**< \brief (AC_STATUSC) Window 0 Current State */

|

||||

#define AC_STATUSC_WSTATE0_Msk (_U_(0x3) << AC_STATUSC_WSTATE0_Pos)

|

||||

#define AC_STATUSC_WSTATE0(value) (AC_STATUSC_WSTATE0_Msk & ((value) << AC_STATUSC_WSTATE0_Pos))

|

||||

#define AC_STATUSC_WSTATE0_ABOVE_Val _U_(0x0) /**< \brief (AC_STATUSC) Signal is above window */

|

||||

#define AC_STATUSC_WSTATE0_INSIDE_Val _U_(0x1) /**< \brief (AC_STATUSC) Signal is inside window */

|

||||

#define AC_STATUSC_WSTATE0_BELOW_Val _U_(0x2) /**< \brief (AC_STATUSC) Signal is below window */

|

||||

#define AC_STATUSC_WSTATE0_ABOVE (AC_STATUSC_WSTATE0_ABOVE_Val << AC_STATUSC_WSTATE0_Pos)

|

||||

#define AC_STATUSC_WSTATE0_INSIDE (AC_STATUSC_WSTATE0_INSIDE_Val << AC_STATUSC_WSTATE0_Pos)

|

||||

#define AC_STATUSC_WSTATE0_BELOW (AC_STATUSC_WSTATE0_BELOW_Val << AC_STATUSC_WSTATE0_Pos)

|

||||

#define AC_STATUSC_MASK _U_(0x33) /**< \brief (AC_STATUSC) MASK Register */

|

||||

|

||||

/* -------- AC_WINCTRL : (AC Offset: 0x0C) (R/W 8) Window Control -------- */

|

||||

#if !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__))

|

||||

typedef union {

|

||||

struct {

|

||||

uint8_t WEN0:1; /*!< bit: 0 Window 0 Mode Enable */

|

||||

uint8_t WINTSEL0:2; /*!< bit: 1.. 2 Window 0 Interrupt Selection */

|

||||

uint8_t :5; /*!< bit: 3.. 7 Reserved */

|

||||

} bit; /*!< Structure used for bit access */

|

||||

uint8_t reg; /*!< Type used for register access */

|

||||

} AC_WINCTRL_Type;

|

||||

#endif /* !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__)) */

|

||||

|

||||

#define AC_WINCTRL_OFFSET 0x0C /**< \brief (AC_WINCTRL offset) Window Control */

|

||||

#define AC_WINCTRL_RESETVALUE _U_(0x00) /**< \brief (AC_WINCTRL reset_value) Window Control */

|

||||

|

||||

#define AC_WINCTRL_WEN0_Pos 0 /**< \brief (AC_WINCTRL) Window 0 Mode Enable */

|

||||

#define AC_WINCTRL_WEN0 (_U_(0x1) << AC_WINCTRL_WEN0_Pos)

|

||||

#define AC_WINCTRL_WINTSEL0_Pos 1 /**< \brief (AC_WINCTRL) Window 0 Interrupt Selection */

|

||||

#define AC_WINCTRL_WINTSEL0_Msk (_U_(0x3) << AC_WINCTRL_WINTSEL0_Pos)

|

||||

#define AC_WINCTRL_WINTSEL0(value) (AC_WINCTRL_WINTSEL0_Msk & ((value) << AC_WINCTRL_WINTSEL0_Pos))

|

||||

#define AC_WINCTRL_WINTSEL0_ABOVE_Val _U_(0x0) /**< \brief (AC_WINCTRL) Interrupt on signal above window */

|

||||

#define AC_WINCTRL_WINTSEL0_INSIDE_Val _U_(0x1) /**< \brief (AC_WINCTRL) Interrupt on signal inside window */

|

||||

#define AC_WINCTRL_WINTSEL0_BELOW_Val _U_(0x2) /**< \brief (AC_WINCTRL) Interrupt on signal below window */

|

||||

#define AC_WINCTRL_WINTSEL0_OUTSIDE_Val _U_(0x3) /**< \brief (AC_WINCTRL) Interrupt on signal outside window */

|

||||

#define AC_WINCTRL_WINTSEL0_ABOVE (AC_WINCTRL_WINTSEL0_ABOVE_Val << AC_WINCTRL_WINTSEL0_Pos)

|

||||

#define AC_WINCTRL_WINTSEL0_INSIDE (AC_WINCTRL_WINTSEL0_INSIDE_Val << AC_WINCTRL_WINTSEL0_Pos)

|

||||

#define AC_WINCTRL_WINTSEL0_BELOW (AC_WINCTRL_WINTSEL0_BELOW_Val << AC_WINCTRL_WINTSEL0_Pos)

|

||||

#define AC_WINCTRL_WINTSEL0_OUTSIDE (AC_WINCTRL_WINTSEL0_OUTSIDE_Val << AC_WINCTRL_WINTSEL0_Pos)

|

||||

#define AC_WINCTRL_MASK _U_(0x07) /**< \brief (AC_WINCTRL) MASK Register */

|

||||

|

||||

/* -------- AC_COMPCTRL : (AC Offset: 0x10) (R/W 32) Comparator Control n -------- */

|

||||

#if !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__))

|

||||

typedef union {

|

||||

struct {

|

||||

uint32_t ENABLE:1; /*!< bit: 0 Enable */

|

||||

uint32_t SINGLE:1; /*!< bit: 1 Single-Shot Mode */

|

||||

uint32_t SPEED:2; /*!< bit: 2.. 3 Speed Selection */

|

||||

uint32_t :1; /*!< bit: 4 Reserved */

|

||||

uint32_t INTSEL:2; /*!< bit: 5.. 6 Interrupt Selection */

|

||||

uint32_t :1; /*!< bit: 7 Reserved */

|

||||

uint32_t MUXNEG:3; /*!< bit: 8..10 Negative Input Mux Selection */

|

||||

uint32_t :1; /*!< bit: 11 Reserved */

|

||||

uint32_t MUXPOS:2; /*!< bit: 12..13 Positive Input Mux Selection */

|

||||

uint32_t :1; /*!< bit: 14 Reserved */

|

||||

uint32_t SWAP:1; /*!< bit: 15 Swap Inputs and Invert */

|

||||

uint32_t OUT:2; /*!< bit: 16..17 Output */

|

||||

uint32_t :1; /*!< bit: 18 Reserved */

|

||||

uint32_t HYST:1; /*!< bit: 19 Hysteresis Enable */

|

||||

uint32_t :4; /*!< bit: 20..23 Reserved */

|

||||

uint32_t FLEN:3; /*!< bit: 24..26 Filter Length */

|

||||

uint32_t :5; /*!< bit: 27..31 Reserved */

|

||||

} bit; /*!< Structure used for bit access */

|

||||

uint32_t reg; /*!< Type used for register access */

|

||||

} AC_COMPCTRL_Type;

|

||||

#endif /* !(defined(__ASSEMBLY__) || defined(__IAR_SYSTEMS_ASM__)) */

|

||||

|

||||

#define AC_COMPCTRL_OFFSET 0x10 /**< \brief (AC_COMPCTRL offset) Comparator Control n */

|

||||

#define AC_COMPCTRL_RESETVALUE _U_(0x00000000) /**< \brief (AC_COMPCTRL reset_value) Comparator Control n */

|

||||

|

||||

#define AC_COMPCTRL_ENABLE_Pos 0 /**< \brief (AC_COMPCTRL) Enable */

|

||||

#define AC_COMPCTRL_ENABLE (_U_(0x1) << AC_COMPCTRL_ENABLE_Pos)

|

||||

#define AC_COMPCTRL_SINGLE_Pos 1 /**< \brief (AC_COMPCTRL) Single-Shot Mode */

|

||||

#define AC_COMPCTRL_SINGLE (_U_(0x1) << AC_COMPCTRL_SINGLE_Pos)

|

||||

#define AC_COMPCTRL_SPEED_Pos 2 /**< \brief (AC_COMPCTRL) Speed Selection */

|

||||

#define AC_COMPCTRL_SPEED_Msk (_U_(0x3) << AC_COMPCTRL_SPEED_Pos)

|

||||

#define AC_COMPCTRL_SPEED(value) (AC_COMPCTRL_SPEED_Msk & ((value) << AC_COMPCTRL_SPEED_Pos))

|

||||

#define AC_COMPCTRL_SPEED_LOW_Val _U_(0x0) /**< \brief (AC_COMPCTRL) Low speed */

|

||||

#define AC_COMPCTRL_SPEED_HIGH_Val _U_(0x1) /**< \brief (AC_COMPCTRL) High speed */

|

||||

#define AC_COMPCTRL_SPEED_LOW (AC_COMPCTRL_SPEED_LOW_Val << AC_COMPCTRL_SPEED_Pos)

|

||||

#define AC_COMPCTRL_SPEED_HIGH (AC_COMPCTRL_SPEED_HIGH_Val << AC_COMPCTRL_SPEED_Pos)

|

||||

#define AC_COMPCTRL_INTSEL_Pos 5 /**< \brief (AC_COMPCTRL) Interrupt Selection */

|

||||

#define AC_COMPCTRL_INTSEL_Msk (_U_(0x3) << AC_COMPCTRL_INTSEL_Pos)

|

||||

#define AC_COMPCTRL_INTSEL(value) (AC_COMPCTRL_INTSEL_Msk & ((value) << AC_COMPCTRL_INTSEL_Pos))

|

||||

#define AC_COMPCTRL_INTSEL_TOGGLE_Val _U_(0x0) /**< \brief (AC_COMPCTRL) Interrupt on comparator output toggle */

|

||||

#define AC_COMPCTRL_INTSEL_RISING_Val _U_(0x1) /**< \brief (AC_COMPCTRL) Interrupt on comparator output rising */

|

||||

#define AC_COMPCTRL_INTSEL_FALLING_Val _U_(0x2) /**< \brief (AC_COMPCTRL) Interrupt on comparator output falling */

|

||||

#define AC_COMPCTRL_INTSEL_EOC_Val _U_(0x3) /**< \brief (AC_COMPCTRL) Interrupt on end of comparison (single-shot mode only) */

|

||||

#define AC_COMPCTRL_INTSEL_TOGGLE (AC_COMPCTRL_INTSEL_TOGGLE_Val << AC_COMPCTRL_INTSEL_Pos)

|

||||

#define AC_COMPCTRL_INTSEL_RISING (AC_COMPCTRL_INTSEL_RISING_Val << AC_COMPCTRL_INTSEL_Pos)

|

||||

#define AC_COMPCTRL_INTSEL_FALLING (AC_COMPCTRL_INTSEL_FALLING_Val << AC_COMPCTRL_INTSEL_Pos)

|

||||

#define AC_COMPCTRL_INTSEL_EOC (AC_COMPCTRL_INTSEL_EOC_Val << AC_COMPCTRL_INTSEL_Pos)

|

||||

#define AC_COMPCTRL_MUXNEG_Pos 8 /**< \brief (AC_COMPCTRL) Negative Input Mux Selection */

|

||||

#define AC_COMPCTRL_MUXNEG_Msk (_U_(0x7) << AC_COMPCTRL_MUXNEG_Pos)

|

||||

#define AC_COMPCTRL_MUXNEG(value) (AC_COMPCTRL_MUXNEG_Msk & ((value) << AC_COMPCTRL_MUXNEG_Pos))

|

||||

#define AC_COMPCTRL_MUXNEG_PIN0_Val _U_(0x0) /**< \brief (AC_COMPCTRL) I/O pin 0 */

|

||||

#define AC_COMPCTRL_MUXNEG_PIN1_Val _U_(0x1) /**< \brief (AC_COMPCTRL) I/O pin 1 */

|

||||

#define AC_COMPCTRL_MUXNEG_PIN2_Val _U_(0x2) /**< \brief (AC_COMPCTRL) I/O pin 2 */

|

||||

#define AC_COMPCTRL_MUXNEG_PIN3_Val _U_(0x3) /**< \brief (AC_COMPCTRL) I/O pin 3 */

|

||||

#define AC_COMPCTRL_MUXNEG_GND_Val _U_(0x4) /**< \brief (AC_COMPCTRL) Ground */

|

||||

#define AC_COMPCTRL_MUXNEG_VSCALE_Val _U_(0x5) /**< \brief (AC_COMPCTRL) VDD scaler */

|

||||

#define AC_COMPCTRL_MUXNEG_BANDGAP_Val _U_(0x6) /**< \brief (AC_COMPCTRL) Internal bandgap voltage */

|

||||

#define AC_COMPCTRL_MUXNEG_DAC_Val _U_(0x7) /**< \brief (AC_COMPCTRL) DAC output */

|

||||

#define AC_COMPCTRL_MUXNEG_PIN0 (AC_COMPCTRL_MUXNEG_PIN0_Val << AC_COMPCTRL_MUXNEG_Pos)

|

||||

#define AC_COMPCTRL_MUXNEG_PIN1 (AC_COMPCTRL_MUXNEG_PIN1_Val << AC_COMPCTRL_MUXNEG_Pos)

|

||||

#define AC_COMPCTRL_MUXNEG_PIN2 (AC_COMPCTRL_MUXNEG_PIN2_Val << AC_COMPCTRL_MUXNEG_Pos)

|

||||

#define AC_COMPCTRL_MUXNEG_PIN3 (AC_COMPCTRL_MUXNEG_PIN3_Val << AC_COMPCTRL_MUXNEG_Pos)

|

||||

#define AC_COMPCTRL_MUXNEG_GND (AC_COMPCTRL_MUXNEG_GND_Val << AC_COMPCTRL_MUXNEG_Pos)

|

||||

#define AC_COMPCTRL_MUXNEG_VSCALE (AC_COMPCTRL_MUXNEG_VSCALE_Val << AC_COMPCTRL_MUXNEG_Pos)

|

||||

#define AC_COMPCTRL_MUXNEG_BANDGAP (AC_COMPCTRL_MUXNEG_BANDGAP_Val << AC_COMPCTRL_MUXNEG_Pos)

|

||||

#define AC_COMPCTRL_MUXNEG_DAC (AC_COMPCTRL_MUXNEG_DAC_Val << AC_COMPCTRL_MUXNEG_Pos)

|

||||

#define AC_COMPCTRL_MUXPOS_Pos 12 /**< \brief (AC_COMPCTRL) Positive Input Mux Selection */

|

||||

#define AC_COMPCTRL_MUXPOS_Msk (_U_(0x3) << AC_COMPCTRL_MUXPOS_Pos)

|

||||

#define AC_COMPCTRL_MUXPOS(value) (AC_COMPCTRL_MUXPOS_Msk & ((value) << AC_COMPCTRL_MUXPOS_Pos))

|

||||

#define AC_COMPCTRL_MUXPOS_PIN0_Val _U_(0x0) /**< \brief (AC_COMPCTRL) I/O pin 0 */

|

||||

#define AC_COMPCTRL_MUXPOS_PIN1_Val _U_(0x1) /**< \brief (AC_COMPCTRL) I/O pin 1 */

|

||||

#define AC_COMPCTRL_MUXPOS_PIN2_Val _U_(0x2) /**< \brief (AC_COMPCTRL) I/O pin 2 */

|

||||

#define AC_COMPCTRL_MUXPOS_PIN3_Val _U_(0x3) /**< \brief (AC_COMPCTRL) I/O pin 3 */

|

||||