mirror of

https://github.com/RIOT-OS/RIOT.git

synced 2024-12-29 04:50:03 +01:00

boards/samd20-xpro: add support for SAM D20 Xplained Pro

This commit is contained in:

parent

f11fc64af6

commit

33fec8b9dc

22

boards/samd20-xpro/Kconfig

Normal file

22

boards/samd20-xpro/Kconfig

Normal file

@ -0,0 +1,22 @@

|

||||

# Copyright (c) 2020 HAW Hamburg

|

||||

#

|

||||

# This file is subject to the terms and conditions of the GNU Lesser

|

||||

# General Public License v2.1. See the file LICENSE in the top level

|

||||

# directory for more details.

|

||||

|

||||

config BOARD

|

||||

default "samd20-xpro" if BOARD_SAMD20_XPRO

|

||||

|

||||

config BOARD_SAMD20_XPRO

|

||||

bool

|

||||

default y

|

||||

select CPU_MODEL_SAMD20J18

|

||||

select HAS_PERIPH_ADC

|

||||

select HAS_PERIPH_DAC

|

||||

select HAS_PERIPH_I2C

|

||||

select HAS_PERIPH_PWM

|

||||

select HAS_PERIPH_RTC

|

||||

select HAS_PERIPH_RTT

|

||||

select HAS_PERIPH_SPI

|

||||

select HAS_PERIPH_TIMER

|

||||

select HAS_PERIPH_UART

|

||||

3

boards/samd20-xpro/Makefile

Normal file

3

boards/samd20-xpro/Makefile

Normal file

@ -0,0 +1,3 @@

|

||||

MODULE = board

|

||||

|

||||

include $(RIOTBASE)/Makefile.base

|

||||

3

boards/samd20-xpro/Makefile.dep

Normal file

3

boards/samd20-xpro/Makefile.dep

Normal file

@ -0,0 +1,3 @@

|

||||

ifneq (,$(filter saul_default,$(USEMODULE)))

|

||||

USEMODULE += saul_gpio

|

||||

endif

|

||||

13

boards/samd20-xpro/Makefile.features

Normal file

13

boards/samd20-xpro/Makefile.features

Normal file

@ -0,0 +1,13 @@

|

||||

CPU = samd21

|

||||

CPU_MODEL = samd20j18

|

||||

|

||||

# Put defined MCU peripherals here (in alphabetical order)

|

||||

FEATURES_PROVIDED += periph_adc

|

||||

FEATURES_PROVIDED += periph_dac

|

||||

FEATURES_PROVIDED += periph_i2c

|

||||

FEATURES_PROVIDED += periph_pwm

|

||||

FEATURES_PROVIDED += periph_rtc

|

||||

FEATURES_PROVIDED += periph_rtt

|

||||

FEATURES_PROVIDED += periph_spi

|

||||

FEATURES_PROVIDED += periph_timer

|

||||

FEATURES_PROVIDED += periph_uart

|

||||

1

boards/samd20-xpro/Makefile.include

Normal file

1

boards/samd20-xpro/Makefile.include

Normal file

@ -0,0 +1 @@

|

||||

include $(RIOTMAKE)/boards/sam0.inc.mk

|

||||

35

boards/samd20-xpro/board.c

Normal file

35

boards/samd20-xpro/board.c

Normal file

@ -0,0 +1,35 @@

|

||||

/*

|

||||

* Copyright (C) 2020 ML!PA Consulting GmbH

|

||||

*

|

||||

* This file is subject to the terms and conditions of the GNU Lesser

|

||||

* General Public License v2.1. See the file LICENSE in the top level

|

||||

* directory for more details.

|

||||

*/

|

||||

|

||||

/**

|

||||

* @ingroup boards_samd20-xpro

|

||||

* @{

|

||||

*

|

||||

* @file

|

||||

* @brief Board specific implementations for the Atmel SAM D20 Xplained

|

||||

* Pro board

|

||||

*

|

||||

* @author Benjamin Valentin <benjamin.valentin@ml-pa.com>

|

||||

* @}

|

||||

*/

|

||||

|

||||

#include "board.h"

|

||||

#include "periph/gpio.h"

|

||||

|

||||

void board_init(void)

|

||||

{

|

||||

/* initialize the on-board LED */

|

||||

gpio_init(LED0_PIN, GPIO_OUT);

|

||||

LED0_OFF;

|

||||

|

||||

/* initialize the on-board button */

|

||||

gpio_init(BTN0_PIN, BTN0_MODE);

|

||||

|

||||

/* initialize the CPU */

|

||||

cpu_init();

|

||||

}

|

||||

2

boards/samd20-xpro/dist/openocd.cfg

vendored

Normal file

2

boards/samd20-xpro/dist/openocd.cfg

vendored

Normal file

@ -0,0 +1,2 @@

|

||||

source [find target/at91samdXX.cfg]

|

||||

$_TARGETNAME configure -rtos auto

|

||||

85

boards/samd20-xpro/doc.txt

Normal file

85

boards/samd20-xpro/doc.txt

Normal file

@ -0,0 +1,85 @@

|

||||

/**

|

||||

@defgroup boards_samd20-xpro Atmel SAM D20 Xplained Pro

|

||||

@ingroup boards

|

||||

@brief Support for the Atmel SAM D20 Xplained Pro board.

|

||||

|

||||

## Overview

|

||||

|

||||

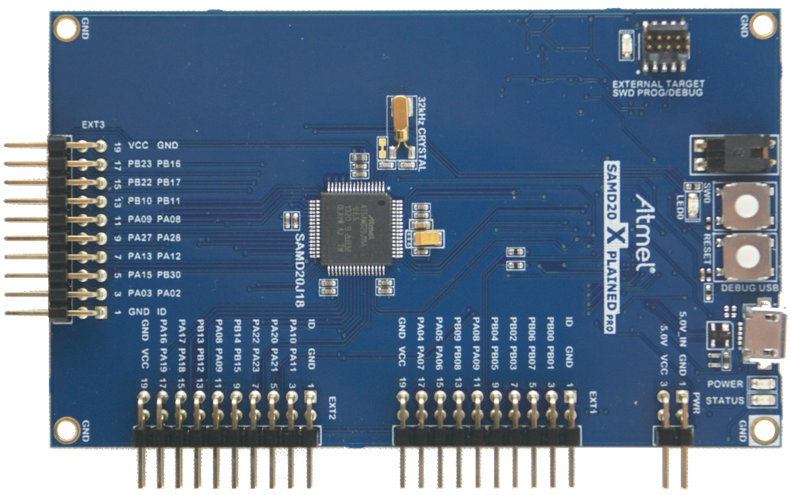

The `SAMD20 Xplained Pro` is an ultra-low power evaluation board by Atmel

|

||||

featuring an ATSAMD20J18 SoC. The SoC includes a SAMD20 ARM Cortex-M0+ micro-

|

||||

controller. For programming the MCU comes with 32Kb of RAM and 256Kb of flash

|

||||

memory.

|

||||

|

||||

## Hardware

|

||||

|

||||

|

||||

|

||||

|

||||

### MCU

|

||||

| MCU | ATSAMD20J18A |

|

||||

|:-------------- |:--------------------------------- |

|

||||

| Family | ARM Cortex-M0+ |

|

||||

| Vendor | Atmel |

|

||||

| RAM | 32 KiB |

|

||||

| Flash | 256 KiB |

|

||||

| Frequency | up to 48MHz |

|

||||

| FPU | no |

|

||||

| Timers | 8 (16-bit) |

|

||||

| ADCs | 1x 12-bit (20 channels) |

|

||||

| UARTs | max 6 (shared with SPI and I2C) |

|

||||

| SPIs | max 6 (see UART) |

|

||||

| I2Cs | max 6 (see UART) |

|

||||

| Vcc | 1.62V - 3.63V |

|

||||

| Datasheet | [Datasheet](http://ww1.microchip.com/downloads/en/DeviceDoc/SAM_D20_%20Family_Datasheet_DS60001504C.pdf) |

|

||||

| Board Manual | [Board Manual](http://ww1.microchip.com/downloads/en/DeviceDoc/Atmel-42102-SAMD20-Xplained-Pro_User-Guide.pdf)|

|

||||

|

||||

### User Interface

|

||||

|

||||

1 User button and 1 LED:

|

||||

|

||||

| Device | PIN |

|

||||

|:------------- |:----- |

|

||||

| LED0 | PA14 |

|

||||

| SW0 (button) | PA15 |

|

||||

|

||||

## Flashing the device

|

||||

|

||||

Connect the device to your Micro-USB cable using the port labeled as *DEBUG

|

||||

USB*.

|

||||

|

||||

The standard method for flashing RIOT to the samd20-xpro is using OpenOCD.

|

||||

|

||||

Refer to https://github.com/RIOT-OS/RIOT/wiki/OpenOCD for general

|

||||

instructions on building OpenOCD and make sure "cmsis-dap" and "hidapi-libusb"

|

||||

are enabled.

|

||||

|

||||

On Linux you will have to add a **udev** rule for hidraw, like

|

||||

```

|

||||

bash

|

||||

echo 'KERNEL=="hidraw*", SUBSYSTEM=="hidraw", MODE="0664", GROUP="plugdev"' \

|

||||

| sudo tee -a /etc/udev/rules.d/99-usb.rules

|

||||

sudo service udev restart

|

||||

```

|

||||

|

||||

### Arch Linux

|

||||

With yaourt:

|

||||

```

|

||||

yaourt -S hidapi-git

|

||||

yaourt -S openocd-git

|

||||

# edit PKGBUILD, add "cmsis-dap hidapi-libusb" to "_features"

|

||||

```

|

||||

|

||||

### Ubuntu

|

||||

Although this refers to setting up the SAMR21, this guide is still very

|

||||

helpful to understanding how to set up a solid RIOT development environment for

|

||||

the SAMD20: http://watr.li/samr21-dev-setup-ubuntu.html

|

||||

|

||||

## Supported Toolchains

|

||||

|

||||

For using the samd20-xpro board we strongly recommend the usage of the

|

||||

[GNU Tools for ARM Embedded Processors](https://launchpad.net/gcc-arm-embedded)

|

||||

toolchain.

|

||||

|

||||

## Known Issues / Problems

|

||||

|

||||

*/

|

||||

72

boards/samd20-xpro/include/board.h

Normal file

72

boards/samd20-xpro/include/board.h

Normal file

@ -0,0 +1,72 @@

|

||||

/*

|

||||

* Copyright (C) 2020 ML!PA Consulting GmbH

|

||||

*

|

||||

* This file is subject to the terms and conditions of the GNU Lesser

|

||||

* General Public License v2.1. See the file LICENSE in the top level

|

||||

* directory for more details.

|

||||

*/

|

||||

|

||||

/**

|

||||

* @ingroup boards_samd20-xpro

|

||||

* @{

|

||||

*

|

||||

* @file

|

||||

* @brief Board specific definitions for the Atmel SAM D20 Xplained Pro

|

||||

* board

|

||||

*

|

||||

* @author Benjamin Valentin <benjamin.valentin@ml-pa.com>

|

||||

*/

|

||||

|

||||

#ifndef BOARD_H

|

||||

#define BOARD_H

|

||||

|

||||

#include "cpu.h"

|

||||

#include "periph_conf.h"

|

||||

#include "periph_cpu.h"

|

||||

|

||||

#ifdef __cplusplus

|

||||

extern "C" {

|

||||

#endif

|

||||

|

||||

/**

|

||||

* @name xtimer configuration

|

||||

* @{

|

||||

*/

|

||||

#define XTIMER_DEV TIMER_DEV(0)

|

||||

#define XTIMER_CHAN (0)

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name LED pin definitions and handlers

|

||||

* @{

|

||||

*/

|

||||

#define LED0_PIN GPIO_PIN(PA, 14)

|

||||

|

||||

#define LED_PORT PORT->Group[PA]

|

||||

#define LED0_MASK (1 << 14)

|

||||

|

||||

#define LED0_ON (LED_PORT.OUTCLR.reg = LED0_MASK)

|

||||

#define LED0_OFF (LED_PORT.OUTSET.reg = LED0_MASK)

|

||||

#define LED0_TOGGLE (LED_PORT.OUTTGL.reg = LED0_MASK)

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name SW0 (Button) pin definitions

|

||||

* @{

|

||||

*/

|

||||

#define BTN0_PORT PORT->Group[PA]

|

||||

#define BTN0_PIN GPIO_PIN(PA, 15)

|

||||

#define BTN0_MODE GPIO_IN_PU

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @brief Initialize board specific hardware, including clock, LEDs and std-IO

|

||||

*/

|

||||

void board_init(void);

|

||||

|

||||

#ifdef __cplusplus

|

||||

}

|

||||

#endif

|

||||

|

||||

#endif /* BOARD_H */

|

||||

/** @} */

|

||||

53

boards/samd20-xpro/include/gpio_params.h

Normal file

53

boards/samd20-xpro/include/gpio_params.h

Normal file

@ -0,0 +1,53 @@

|

||||

/*

|

||||

* Copyright (C) 2020 ML!PA Consulting GmbH

|

||||

*

|

||||

* This file is subject to the terms and conditions of the GNU Lesser

|

||||

* General Public License v2.1. See the file LICENSE in the top level

|

||||

* directory for more details.

|

||||

*/

|

||||

|

||||

/**

|

||||

* @ingroup boards_samd20-xpro

|

||||

* @{

|

||||

*

|

||||

* @file

|

||||

* @brief Board specific configuration of direct mapped GPIOs

|

||||

*

|

||||

* @author Benjamin Valentin <benjamin.valentin@ml-pa.com>

|

||||

*/

|

||||

|

||||

#ifndef GPIO_PARAMS_H

|

||||

#define GPIO_PARAMS_H

|

||||

|

||||

#include "board.h"

|

||||

#include "saul/periph.h"

|

||||

|

||||

#ifdef __cplusplus

|

||||

extern "C" {

|

||||

#endif

|

||||

|

||||

/**

|

||||

* @brief GPIO pin configuration

|

||||

*/

|

||||

static const saul_gpio_params_t saul_gpio_params[] =

|

||||

{

|

||||

{

|

||||

.name = "LED(orange)",

|

||||

.pin = LED0_PIN,

|

||||

.mode = GPIO_OUT,

|

||||

.flags = SAUL_GPIO_INVERTED,

|

||||

},

|

||||

{

|

||||

.name = "Button(SW0)",

|

||||

.pin = BTN0_PIN,

|

||||

.mode = BTN0_MODE,

|

||||

.flags = SAUL_GPIO_INVERTED,

|

||||

},

|

||||

};

|

||||

|

||||

#ifdef __cplusplus

|

||||

}

|

||||

#endif

|

||||

|

||||

#endif /* GPIO_PARAMS_H */

|

||||

/** @} */

|

||||

317

boards/samd20-xpro/include/periph_conf.h

Normal file

317

boards/samd20-xpro/include/periph_conf.h

Normal file

@ -0,0 +1,317 @@

|

||||

/*

|

||||

* Copyright (C) 2020 ML!PA Consulting GmbH

|

||||

*

|

||||

* This file is subject to the terms and conditions of the GNU Lesser

|

||||

* General Public License v2.1. See the file LICENSE in the top level

|

||||

* directory for more details.

|

||||

*/

|

||||

|

||||

/**

|

||||

* @ingroup boards_samd20-xpro

|

||||

* @{

|

||||

*

|

||||

* @file

|

||||

* @brief Configuration of CPU peripherals for the Atmel SAM D20 Xplained

|

||||

* Pro board

|

||||

*

|

||||

* @author Travis Griggs <travisgriggs@gmail.com>

|

||||

* @author Dan Evans <photonthunder@gmail.com>

|

||||

* @author Benjamin Valentin <benjamin.valentin@ml-pa.com>

|

||||

*/

|

||||

|

||||

#ifndef PERIPH_CONF_H

|

||||

#define PERIPH_CONF_H

|

||||

|

||||

#include <stdint.h>

|

||||

|

||||

#include "cpu.h"

|

||||

#include "periph_cpu.h"

|

||||

|

||||

#ifdef __cplusplus

|

||||

extern "C" {

|

||||

#endif

|

||||

|

||||

/**

|

||||

* @name External oscillator and clock configuration

|

||||

*

|

||||

* There are three choices for selection of CORECLOCK:

|

||||

*

|

||||

* - usage of the 48 MHz DFLL fed by external oscillator running at 32 kHz

|

||||

* - usage of the PLL fed by the internal 8MHz oscillator divided by 8

|

||||

* - usage of the internal 8MHz oscillator directly, divided by N if needed

|

||||

*

|

||||

*

|

||||

* The PLL option allows for the usage of a wider frequency range and a more

|

||||

* stable clock with less jitter. This is why this option is default.

|

||||

*

|

||||

* The target frequency is computed from the PLL multiplier and the PLL divisor.

|

||||

* Use the following formula to compute your values:

|

||||

*

|

||||

* CORECLOCK = ((PLL_MUL + 1) * 1MHz) / PLL_DIV

|

||||

*

|

||||

* NOTE: The PLL circuit does not run with less than 32MHz while the maximum PLL

|

||||

* frequency is 96MHz. So PLL_MULL must be between 31 and 95!

|

||||

*

|

||||

*

|

||||

* The internal Oscillator used directly can lead to a slightly better power

|

||||

* efficiency to the cost of a less stable clock. Use this option when you know

|

||||

* what you are doing! The actual core frequency is adjusted as follows:

|

||||

*

|

||||

* CORECLOCK = 8MHz / DIV

|

||||

*

|

||||

* NOTE: A core clock frequency below 1MHz is not recommended

|

||||

*

|

||||

* @{

|

||||

*/

|

||||

#define CLOCK_USE_PLL (0)

|

||||

#define CLOCK_USE_XOSC32_DFLL (1)

|

||||

/*

|

||||

* 0: use XOSC32K (always 32.768kHz) to clock GCLK2

|

||||

* 1: use OSCULP32K factory calibrated (~32.768kHz) to clock GCLK2

|

||||

*

|

||||

* OSCULP32K is factory calibrated to be around 32.768kHz but this values can

|

||||

* be of by a couple off % points, so prefer XOSC32K as default configuration.

|

||||

*/

|

||||

#define GEN2_ULP32K (0)

|

||||

|

||||

#if CLOCK_USE_PLL

|

||||

/* edit these values to adjust the PLL output frequency */

|

||||

#define CLOCK_PLL_MUL (47U) /* must be >= 31 & <= 95 */

|

||||

#define CLOCK_PLL_DIV (1U) /* adjust to your needs */

|

||||

/* generate the actual used core clock frequency */

|

||||

#define CLOCK_CORECLOCK (((CLOCK_PLL_MUL + 1) * 1000000U) / CLOCK_PLL_DIV)

|

||||

#elif CLOCK_USE_XOSC32_DFLL

|

||||

/* Settings for 32 kHz external oscillator and 48 MHz DFLL */

|

||||

#define CLOCK_CORECLOCK (48000000U)

|

||||

#define CLOCK_XOSC32K (32768UL)

|

||||

#define CLOCK_8MHZ (1)

|

||||

#else

|

||||

/* edit this value to your needs */

|

||||

#define CLOCK_DIV (1U)

|

||||

/* generate the actual core clock frequency */

|

||||

#define CLOCK_CORECLOCK (8000000 / CLOCK_DIV)

|

||||

#endif

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name Timer peripheral configuration

|

||||

* @{

|

||||

*/

|

||||

static const tc32_conf_t timer_config[] = {

|

||||

{ /* Timer 0 - System Clock */

|

||||

.dev = TC0,

|

||||

.irq = TC0_IRQn,

|

||||

.pm_mask = PM_APBCMASK_TC0 | PM_APBCMASK_TC1,

|

||||

.gclk_ctrl = GCLK_CLKCTRL_ID_TC0_TC1,

|

||||

#if CLOCK_USE_PLL || CLOCK_USE_XOSC32_DFLL

|

||||

.gclk_src = SAM0_GCLK_1MHZ,

|

||||

#else

|

||||

.gclk_src = SAM0_GCLK_MAIN,

|

||||

#endif

|

||||

.flags = TC_CTRLA_MODE_COUNT32,

|

||||

},

|

||||

{ /* Timer 1 */

|

||||

.dev = TC4,

|

||||

.irq = TC4_IRQn,

|

||||

.pm_mask = PM_APBCMASK_TC4 | PM_APBCMASK_TC5,

|

||||

.gclk_ctrl = GCLK_CLKCTRL_ID_TC4_TC5,

|

||||

#if CLOCK_USE_PLL || CLOCK_USE_XOSC32_DFLL

|

||||

.gclk_src = SAM0_GCLK_1MHZ,

|

||||

#else

|

||||

.gclk_src = SAM0_GCLK_MAIN,

|

||||

#endif

|

||||

.flags = TC_CTRLA_MODE_COUNT32,

|

||||

}

|

||||

};

|

||||

|

||||

/* interrupt function name mapping */

|

||||

#define TIMER_0_ISR isr_tc0

|

||||

#define TIMER_1_ISR isr_tc4

|

||||

|

||||

#define TIMER_NUMOF ARRAY_SIZE(timer_config)

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name UART configuration

|

||||

* @{

|

||||

*/

|

||||

static const uart_conf_t uart_config[] = {

|

||||

{ /* Virtual COM Port */

|

||||

.dev = &SERCOM3->USART,

|

||||

.rx_pin = GPIO_PIN(PA,25),

|

||||

.tx_pin = GPIO_PIN(PA,24),

|

||||

#ifdef MODULE_PERIPH_UART_HW_FC

|

||||

.rts_pin = GPIO_UNDEF,

|

||||

.cts_pin = GPIO_UNDEF,

|

||||

#endif

|

||||

.mux = GPIO_MUX_C,

|

||||

.rx_pad = UART_PAD_RX_3,

|

||||

.tx_pad = UART_PAD_TX_2,

|

||||

.flags = UART_FLAG_NONE,

|

||||

.gclk_src = SAM0_GCLK_MAIN,

|

||||

},

|

||||

{ /* EXT1 */

|

||||

.dev = &SERCOM4->USART,

|

||||

.rx_pin = GPIO_PIN(PB,9),

|

||||

.tx_pin = GPIO_PIN(PB,8),

|

||||

#ifdef MODULE_PERIPH_UART_HW_FC

|

||||

.rts_pin = GPIO_UNDEF,

|

||||

.cts_pin = GPIO_UNDEF,

|

||||

#endif

|

||||

.mux = GPIO_MUX_D,

|

||||

.rx_pad = UART_PAD_RX_1,

|

||||

.tx_pad = UART_PAD_TX_0,

|

||||

.flags = UART_FLAG_NONE,

|

||||

.gclk_src = SAM0_GCLK_MAIN,

|

||||

},

|

||||

};

|

||||

|

||||

/* interrupt function name mapping */

|

||||

#define UART_0_ISR isr_sercom3

|

||||

#define UART_1_ISR isr_sercom4

|

||||

|

||||

#define UART_NUMOF ARRAY_SIZE(uart_config)

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name SPI configuration

|

||||

* @{

|

||||

*/

|

||||

static const spi_conf_t spi_config[] = {

|

||||

{ /* EXT1 */

|

||||

.dev = &SERCOM0->SPI,

|

||||

.miso_pin = GPIO_PIN(PA, 4),

|

||||

.mosi_pin = GPIO_PIN(PA, 6),

|

||||

.clk_pin = GPIO_PIN(PA, 7),

|

||||

.miso_mux = GPIO_MUX_D,

|

||||

.mosi_mux = GPIO_MUX_D,

|

||||

.clk_mux = GPIO_MUX_D,

|

||||

.miso_pad = SPI_PAD_MISO_0,

|

||||

.mosi_pad = SPI_PAD_MOSI_2_SCK_3,

|

||||

.gclk_src = SAM0_GCLK_MAIN,

|

||||

},

|

||||

{ /* EXT2 */

|

||||

.dev = &SERCOM1->SPI,

|

||||

.miso_pin = GPIO_PIN(PA, 16),

|

||||

.mosi_pin = GPIO_PIN(PA, 18),

|

||||

.clk_pin = GPIO_PIN(PA, 19),

|

||||

.miso_mux = GPIO_MUX_C,

|

||||

.mosi_mux = GPIO_MUX_C,

|

||||

.clk_mux = GPIO_MUX_C,

|

||||

.miso_pad = SPI_PAD_MISO_0,

|

||||

.mosi_pad = SPI_PAD_MOSI_2_SCK_3,

|

||||

.gclk_src = SAM0_GCLK_MAIN,

|

||||

},

|

||||

{ /* EXT3 */

|

||||

.dev = &SERCOM5->SPI,

|

||||

.miso_pin = GPIO_PIN(PB, 16),

|

||||

.mosi_pin = GPIO_PIN(PB, 22),

|

||||

.clk_pin = GPIO_PIN(PB, 23),

|

||||

.miso_mux = GPIO_MUX_C,

|

||||

.mosi_mux = GPIO_MUX_D,

|

||||

.clk_mux = GPIO_MUX_D,

|

||||

.miso_pad = SPI_PAD_MISO_0,

|

||||

.mosi_pad = SPI_PAD_MOSI_2_SCK_3,

|

||||

.gclk_src = SAM0_GCLK_MAIN,

|

||||

},

|

||||

};

|

||||

|

||||

#define SPI_NUMOF ARRAY_SIZE(spi_config)

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name I2C configuration

|

||||

* @{

|

||||

*/

|

||||

static const i2c_conf_t i2c_config[] = {

|

||||

{

|

||||

.dev = &(SERCOM2->I2CM),

|

||||

.speed = I2C_SPEED_NORMAL,

|

||||

.scl_pin = GPIO_PIN(PA, 9),

|

||||

.sda_pin = GPIO_PIN(PA, 8),

|

||||

.mux = GPIO_MUX_D,

|

||||

.gclk_src = SAM0_GCLK_MAIN,

|

||||

.flags = I2C_FLAG_NONE

|

||||

}

|

||||

};

|

||||

#define I2C_NUMOF ARRAY_SIZE(i2c_config)

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name RTT configuration

|

||||

* @{

|

||||

*/

|

||||

#ifndef RTT_FREQUENCY

|

||||

#define RTT_FREQUENCY (32768U) /* in Hz. For changes see `rtt.c` */

|

||||

#endif

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name PWM configuration

|

||||

* @{

|

||||

*/

|

||||

#define PWM_0_EN 1

|

||||

|

||||

#if PWM_0_EN

|

||||

/* PWM0 channels */

|

||||

static const pwm_conf_chan_t pwm_chan0_config[] = {

|

||||

/* GPIO pin, MUX value, TCC channel */

|

||||

{ GPIO_PIN(PA, 14), GPIO_MUX_E, 0 },

|

||||

};

|

||||

#endif

|

||||

|

||||

/* PWM device configuration */

|

||||

static const pwm_conf_t pwm_config[] = {

|

||||

#if PWM_0_EN

|

||||

{ .tim = TC_CONFIG(TC3),

|

||||

.chan = pwm_chan0_config,

|

||||

.chan_numof = ARRAY_SIZE(pwm_chan0_config),

|

||||

.gclk_src = SAM0_GCLK_1MHZ,

|

||||

},

|

||||

#endif

|

||||

};

|

||||

|

||||

/* number of devices that are actually defined */

|

||||

#define PWM_NUMOF ARRAY_SIZE(pwm_config)

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name ADC Configuration

|

||||

* @{

|

||||

*/

|

||||

|

||||

/* ADC Default values */

|

||||

#define ADC_PRESCALER ADC_CTRLB_PRESCALER_DIV128

|

||||

|

||||

#define ADC_NEG_INPUT ADC_INPUTCTRL_MUXNEG_GND

|

||||

#define ADC_GAIN_FACTOR_DEFAULT ADC_INPUTCTRL_GAIN_1X

|

||||

#define ADC_REF_DEFAULT ADC_REFCTRL_REFSEL_INT1V

|

||||

|

||||

static const adc_conf_chan_t adc_channels[] = {

|

||||

/* port, pin, muxpos */

|

||||

{GPIO_PIN(PB, 0), ADC_INPUTCTRL_MUXPOS_PIN8}, /* EXT1, pin 3 */

|

||||

{GPIO_PIN(PB, 1), ADC_INPUTCTRL_MUXPOS_PIN9}, /* EXT1, pin 4 */

|

||||

{GPIO_PIN(PA, 10), ADC_INPUTCTRL_MUXPOS_PIN18}, /* EXT2, pin 3 */

|

||||

{GPIO_PIN(PA, 11), ADC_INPUTCTRL_MUXPOS_PIN19}, /* EXT2, pin 4 */

|

||||

{GPIO_PIN(PA, 2), ADC_INPUTCTRL_MUXPOS_PIN0}, /* EXT3, pin 3 */

|

||||

{GPIO_PIN(PA, 3), ADC_INPUTCTRL_MUXPOS_PIN1} /* EXT3, pin 4.*/

|

||||

};

|

||||

|

||||

#define ADC_NUMOF ARRAY_SIZE(adc_channels)

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name DAC configuration

|

||||

* @{

|

||||

*/

|

||||

#define DAC_CLOCK SAM0_GCLK_1MHZ

|

||||

/* use Vcc as reference voltage */

|

||||

#define DAC_VREF DAC_CTRLB_REFSEL_AVCC

|

||||

/** @} */

|

||||

|

||||

#ifdef __cplusplus

|

||||

}

|

||||

#endif

|

||||

|

||||

#endif /* PERIPH_CONF_H */

|

||||

/** @} */

|

||||

@ -68,6 +68,7 @@ BOARD_INSUFFICIENT_MEMORY := \

|

||||

remote-pa \

|

||||

remote-reva \

|

||||

remote-revb \

|

||||

samd20-xpro \

|

||||

samd21-xpro \

|

||||

saml10-xpro \

|

||||

saml11-xpro \

|

||||

|

||||

@ -82,6 +82,7 @@ BOARD_INSUFFICIENT_MEMORY := \

|

||||

openlabs-kw41z-mini-256kib \

|

||||

pba-d-01-kw2x \

|

||||

samd10-xmini \

|

||||

samd20-xpro \

|

||||

samd21-xpro \

|

||||

saml10-xpro \

|

||||

saml11-xpro \

|

||||

|

||||

Loading…

Reference in New Issue

Block a user