mirror of

https://github.com/RIOT-OS/RIOT.git

synced 2024-12-29 04:50:03 +01:00

boards: p-nucleo-wb55 initial support

This commit is contained in:

parent

c6e0e7adcb

commit

e220483adc

3

boards/common/stm32/dist/stm32wb.cfg

vendored

Normal file

3

boards/common/stm32/dist/stm32wb.cfg

vendored

Normal file

@ -0,0 +1,3 @@

|

||||

source [find target/stm32wbx.cfg]

|

||||

reset_config srst_only

|

||||

$_TARGETNAME configure -rtos auto

|

||||

@ -47,7 +47,7 @@ static const i2c_conf_t i2c_config[] = {

|

||||

.rcc_mask = RCC_APB1ENR_I2C1EN,

|

||||

.clk = CLOCK_APB1,

|

||||

.irqn = I2C1_EV_IRQn,

|

||||

#elif CPU_FAM_STM32L4

|

||||

#elif CPU_FAM_STM32L4 || CPU_FAM_STM32WB

|

||||

.rcc_mask = RCC_APB1ENR1_I2C1EN,

|

||||

.irqn = I2C1_ER_IRQn,

|

||||

#elif CPU_FAM_STM32F7

|

||||

@ -65,7 +65,7 @@ static const i2c_conf_t i2c_config[] = {

|

||||

|

||||

#if CPU_FAM_STM32F4 || CPU_FAM_STM32F2

|

||||

#define I2C_0_ISR isr_i2c1_ev

|

||||

#elif CPU_FAM_STM32L4 || CPU_FAM_STM32F7

|

||||

#elif CPU_FAM_STM32L4 || CPU_FAM_STM32F7 || CPU_FAM_STM32WB

|

||||

#define I2C_0_ISR isr_i2c1_er

|

||||

#elif CPU_FAM_STM32F0 || CPU_FAM_STM32L0

|

||||

#define I2C_0_ISR isr_i2c1

|

||||

|

||||

@ -37,7 +37,7 @@ static const timer_conf_t timer_config[] = {

|

||||

#else

|

||||

.max = 0xffffffff,

|

||||

#endif

|

||||

#if CPU_FAM_STM32L4

|

||||

#if defined(CPU_FAM_STM32L4) || defined(CPU_FAM_STM32WB)

|

||||

.rcc_mask = RCC_APB1ENR1_TIM2EN,

|

||||

#else

|

||||

.rcc_mask = RCC_APB1ENR_TIM2EN,

|

||||

|

||||

4

boards/p-nucleo-wb55/Makefile

Normal file

4

boards/p-nucleo-wb55/Makefile

Normal file

@ -0,0 +1,4 @@

|

||||

MODULE = board

|

||||

DIRS = $(RIOTBOARD)/common/nucleo

|

||||

|

||||

include $(RIOTBASE)/Makefile.base

|

||||

3

boards/p-nucleo-wb55/Makefile.dep

Normal file

3

boards/p-nucleo-wb55/Makefile.dep

Normal file

@ -0,0 +1,3 @@

|

||||

FEATURES_REQUIRED += periph_lpuart

|

||||

|

||||

include $(RIOTBOARD)/common/nucleo/Makefile.dep

|

||||

16

boards/p-nucleo-wb55/Makefile.features

Normal file

16

boards/p-nucleo-wb55/Makefile.features

Normal file

@ -0,0 +1,16 @@

|

||||

## the cpu to build for

|

||||

CPU = stm32wb

|

||||

CPU_MODEL = stm32wb55rg

|

||||

|

||||

# Put defined MCU peripherals here (in alphabetical order)

|

||||

FEATURES_PROVIDED += periph_i2c

|

||||

FEATURES_PROVIDED += periph_lpuart

|

||||

FEATURES_PROVIDED += periph_rtc

|

||||

FEATURES_PROVIDED += periph_rtt

|

||||

FEATURES_PROVIDED += periph_spi

|

||||

FEATURES_PROVIDED += periph_timer

|

||||

FEATURES_PROVIDED += periph_uart

|

||||

|

||||

# Put other features for this board (in alphabetical order)

|

||||

FEATURES_PROVIDED += arduino

|

||||

FEATURES_PROVIDED += riotboot

|

||||

14

boards/p-nucleo-wb55/Makefile.include

Normal file

14

boards/p-nucleo-wb55/Makefile.include

Normal file

@ -0,0 +1,14 @@

|

||||

# CPU2 defines a restricted memory region. This is not available for

|

||||

# CPU1 linking or general access, for now we define it by its default

|

||||

# value.

|

||||

CPU2_ROM_LEN = 216K

|

||||

|

||||

# CPU2 can define restricted SRAM within SRAM2a and SRAM2b. These subregions

|

||||

# will generate busfaults if accessed by CPU1. For now we will assume that both

|

||||

# SRAM2a regions are completely dedicated to CPU2.

|

||||

CPU2_RAM_LEN = 64K

|

||||

|

||||

OPENOCD_RESET_USE_CONNECT_ASSERT_SRST ?= 1

|

||||

|

||||

# include shared global Nucleo Makefile

|

||||

include $(RIOTBOARD)/common/nucleo/Makefile.include

|

||||

110

boards/p-nucleo-wb55/doc.txt

Normal file

110

boards/p-nucleo-wb55/doc.txt

Normal file

@ -0,0 +1,110 @@

|

||||

/**

|

||||

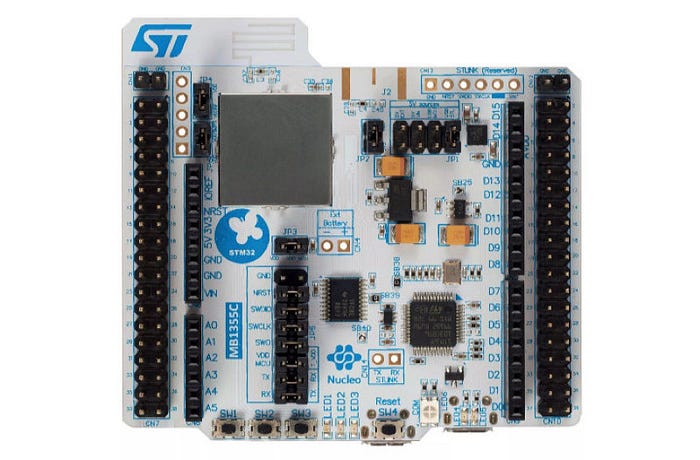

@defgroup boards_p-nucleo-wb55 STM32 p-nucleo-wb55

|

||||

@ingroup boards_common_nucleo

|

||||

@brief Support for the STM32 p-nucleo-wb55

|

||||

|

||||

Hardware

|

||||

========

|

||||

|

||||

|

||||

|

||||

MCU

|

||||

---

|

||||

|

||||

| MCU | STM32WB55RG |

|

||||

|:---------- |:------------------------------- |

|

||||

| Family | ARM Cortex-M4 |

|

||||

| Vendor | ST Microelectronics |

|

||||

| RAM | 256KB |

|

||||

| Flash | 512KB |

|

||||

| Frequency | 64MHz |

|

||||

| FPU | yes |

|

||||

| Timers | 8 (3x 16-bit, 1x 32-bit [TIM5]) |

|

||||

| LPTimers | 2x 16-bit |

|

||||

| ADCs | 1x 19-channel 12-bit |

|

||||

| UARTs | 1 |

|

||||

| LUARTs | 1 |

|

||||

| SPIs | 1 |

|

||||

| I2Cs | 2 |

|

||||

| RTC | 1 |

|

||||

| Vcc | 1.65V - 3.6V |

|

||||

| Datasheet | [Datasheet](https://www.st.com/resource/en/datasheet/stm32wb55cc.pdf)|

|

||||

| Reference Manual | [Reference Manual](https://www.st.com/resource/en/datasheet/stm32wb55cc.pdf) |

|

||||

| User Manual | [User Manual](https://www.st.com/content/ccc/resource/technical/document/user_manual/group1/13/58/22/1a/f2/ff/43/5c/DM00517423/files/DM00517423.pdf/jcr:content/translations/en.DM00517423.pdf) |

|

||||

|

||||

Overview

|

||||

========

|

||||

|

||||

The p-nucleo-wb55 is a multi-protocol wireless and ultra-low-power

|

||||

device embedding a powerful and ultra-low-power radio compliant with the

|

||||

Bluetooth® Low Energy (BLE) SIG specification v5.0 and with IEEE

|

||||

802.15.4-2011 board. It integrates an ARM Cortex-M4 STM32WB55RG microcontroller

|

||||

with 256KB of RAM and 1MB of ROM Flash.

|

||||

|

||||

Flashing the device

|

||||

-------------------

|

||||

|

||||

The ST p-nucleo-wb55 board includes an on-board ST-LINK programmer and can be

|

||||

flashed using OpenOCD.

|

||||

|

||||

@note The latest release of OpenOCD doesn't contain support for this board,

|

||||

so a recent development version must be built from source to be able to flash

|

||||

this board.

|

||||

|

||||

To flash this board, just use the following command:

|

||||

|

||||

```

|

||||

make BOARD=p-nucleo-wb55 flash -C examples/hello-world

|

||||

```

|

||||

|

||||

STDIO

|

||||

-----

|

||||

STDIO is available via the ST-Link programmer.

|

||||

|

||||

Use the `term` target to open a terminal:

|

||||

|

||||

make BOARD=p-nucleo-wb55 -C examples/hello-world term

|

||||

|

||||

|

||||

User Interface

|

||||

--------------

|

||||

|

||||

4 Button:

|

||||

|

||||

| NAME | RESET/SW4 | SW1 | SW2 | SW3 |

|

||||

|:------ |:--------- |:----- |:----- |:----- |

|

||||

| Pin | NRST | PC4 | PD0 | PD1 |

|

||||

|

||||

3 LED:

|

||||

|

||||

| NAME | LED1 | LED2 | LED3 |

|

||||

| ----- | ------ | ------ | ------ |

|

||||

| Color | blue | green | red |

|

||||

| Pin | PB5 | PB0 | PB1 |

|

||||

|

||||

|

||||

Implementation Status

|

||||

---------------------

|

||||

|

||||

| Device | ID | Supported | Comments |

|

||||

|:---------------- |:----------------- |:------- |:------- |

|

||||

| MCU | stm32wb | yes | |

|

||||

| | M0+ co-processor | no | |

|

||||

| | BLE | no | |

|

||||

| | 802.15.4 | no | |

|

||||

| Low-level driver | GPIO | yes | |

|

||||

| | UART | yes | UART1 |

|

||||

| | LPUART | yes | LPUART1 |

|

||||

| | I2C | yes | I2C1 |

|

||||

| | SPI | yes | |

|

||||

| | ADC | yes | |

|

||||

| | RTT | yes | |

|

||||

| | RTC | yes | |

|

||||

| | RNG | yes | |

|

||||

| | Timer | yes | TIM2 |

|

||||

| | WDT | no | |

|

||||

| | USB | no | |

|

||||

| | PWM | no | |

|

||||

| | AES | no | |

|

||||

|

||||

*/

|

||||

73

boards/p-nucleo-wb55/include/arduino_board.h

Normal file

73

boards/p-nucleo-wb55/include/arduino_board.h

Normal file

@ -0,0 +1,73 @@

|

||||

/*

|

||||

* Copyright (C) 2016 Freie Universität Berlin

|

||||

* 2019 Inria

|

||||

*

|

||||

* This file is subject to the terms and conditions of the GNU Lesser

|

||||

* General Public License v2.1. See the file LICENSE in the top level

|

||||

* directory for more details.

|

||||

*/

|

||||

|

||||

/**

|

||||

* @ingroup boards_p-nucleo-wb55

|

||||

* @{

|

||||

*

|

||||

* @file

|

||||

* @brief Board specific configuration for the Arduino API

|

||||

*

|

||||

* @author Hauke Petersen <hauke.petersen@fu-berlin.de>

|

||||

* @author Alexandre Abadie <alexandre.abadie@inria.fr>

|

||||

*/

|

||||

|

||||

#ifndef ARDUINO_BOARD_H

|

||||

#define ARDUINO_BOARD_H

|

||||

|

||||

#include "arduino_pinmap.h"

|

||||

|

||||

#ifdef __cplusplus

|

||||

extern "C" {

|

||||

#endif

|

||||

|

||||

/**

|

||||

* @brief Look-up table for the Arduino's digital pins

|

||||

*/

|

||||

static const gpio_t arduino_pinmap[] = {

|

||||

ARDUINO_PIN_0,

|

||||

ARDUINO_PIN_1,

|

||||

ARDUINO_PIN_2,

|

||||

ARDUINO_PIN_3,

|

||||

ARDUINO_PIN_4,

|

||||

ARDUINO_PIN_5,

|

||||

ARDUINO_PIN_6,

|

||||

ARDUINO_PIN_7,

|

||||

ARDUINO_PIN_8,

|

||||

ARDUINO_PIN_9,

|

||||

ARDUINO_PIN_10,

|

||||

ARDUINO_PIN_11,

|

||||

ARDUINO_PIN_12,

|

||||

ARDUINO_PIN_13,

|

||||

ARDUINO_PIN_A0,

|

||||

ARDUINO_PIN_A1,

|

||||

ARDUINO_PIN_A2,

|

||||

ARDUINO_PIN_A3,

|

||||

ARDUINO_PIN_A4,

|

||||

ARDUINO_PIN_A5,

|

||||

};

|

||||

|

||||

/**

|

||||

* @brief Look-up table for the Arduino's analog pins

|

||||

*/

|

||||

static const adc_t arduino_analog_map[] = {

|

||||

ARDUINO_A0,

|

||||

ARDUINO_A1,

|

||||

ARDUINO_A2,

|

||||

ARDUINO_A3,

|

||||

ARDUINO_A4,

|

||||

ARDUINO_A5,

|

||||

};

|

||||

|

||||

#ifdef __cplusplus

|

||||

}

|

||||

#endif

|

||||

|

||||

#endif /* ARDUINO_BOARD_H */

|

||||

/** @} */

|

||||

80

boards/p-nucleo-wb55/include/arduino_pinmap.h

Normal file

80

boards/p-nucleo-wb55/include/arduino_pinmap.h

Normal file

@ -0,0 +1,80 @@

|

||||

/*

|

||||

* Copyright (C) 2019 Inria

|

||||

*

|

||||

* This file is subject to the terms and conditions of the GNU Lesser

|

||||

* General Public License v2.1. See the file LICENSE in the top level

|

||||

* directory for more details.

|

||||

*/

|

||||

|

||||

/**

|

||||

* @ingroup boards_p-nucleo-wb55

|

||||

* @{

|

||||

*

|

||||

* @file

|

||||

* @brief Mapping from MCU pins to Arduino pins

|

||||

*

|

||||

* You can use the defines in this file for simplified interaction with the

|

||||

* Arduino specific pin numbers.

|

||||

*

|

||||

* @author Alexandre Abadie <alexandre.abadie@inria.fr>

|

||||

* @author Francisco Molina <francois-xavier.molina@inria.fr>

|

||||

*

|

||||

*/

|

||||

|

||||

#ifndef ARDUINO_PINMAP_H

|

||||

#define ARDUINO_PINMAP_H

|

||||

|

||||

#include "periph/gpio.h"

|

||||

#include "periph/adc.h"

|

||||

|

||||

#ifdef __cplusplus

|

||||

extern "C" {

|

||||

#endif

|

||||

|

||||

/**

|

||||

* @brief Mapping of MCU pins to Arduino pins

|

||||

* @{

|

||||

*/

|

||||

#define ARDUINO_PIN_0 GPIO_PIN(PORT_A, 3)

|

||||

#define ARDUINO_PIN_1 GPIO_PIN(PORT_A, 2)

|

||||

#define ARDUINO_PIN_2 GPIO_PIN(PORT_C, 6)

|

||||

#define ARDUINO_PIN_3 GPIO_PIN(PORT_A, 10)

|

||||

#define ARDUINO_PIN_4 GPIO_PIN(PORT_C, 10)

|

||||

#define ARDUINO_PIN_5 GPIO_PIN(PORT_A, 15)

|

||||

#define ARDUINO_PIN_6 GPIO_PIN(PORT_A, 8)

|

||||

#define ARDUINO_PIN_7 GPIO_PIN(PORT_C, 13)

|

||||

#define ARDUINO_PIN_8 GPIO_PIN(PORT_C, 12)

|

||||

#define ARDUINO_PIN_9 GPIO_PIN(PORT_A, 9)

|

||||

#define ARDUINO_PIN_10 GPIO_PIN(PORT_A, 4)

|

||||

#define ARDUINO_PIN_11 GPIO_PIN(PORT_A, 7)

|

||||

#define ARDUINO_PIN_12 GPIO_PIN(PORT_A, 6)

|

||||

#define ARDUINO_PIN_13 GPIO_PIN(PORT_A, 5)

|

||||

#define ARDUINO_PIN_14 GPIO_PIN(PORT_B, 9)

|

||||

#define ARDUINO_PIN_15 GPIO_PIN(PORT_B, 8)

|

||||

|

||||

#define ARDUINO_PIN_A0 GPIO_PIN(PORT_C, 0)

|

||||

#define ARDUINO_PIN_A1 GPIO_PIN(PORT_C, 1)

|

||||

#define ARDUINO_PIN_A2 GPIO_PIN(PORT_A, 1)

|

||||

#define ARDUINO_PIN_A3 GPIO_PIN(PORT_A, 0)

|

||||

#define ARDUINO_PIN_A4 GPIO_PIN(PORT_C, 3)

|

||||

#define ARDUINO_PIN_A5 GPIO_PIN(PORT_C, 2)

|

||||

/** @ */

|

||||

|

||||

/**

|

||||

* @name Mapping of Arduino analog pins to RIOT ADC lines

|

||||

* @{

|

||||

*/

|

||||

#define ARDUINO_A0 ADC_LINE(0)

|

||||

#define ARDUINO_A1 ADC_LINE(1)

|

||||

#define ARDUINO_A2 ADC_LINE(2)

|

||||

#define ARDUINO_A3 ADC_LINE(3)

|

||||

#define ARDUINO_A4 ADC_LINE(4)

|

||||

#define ARDUINO_A5 ADC_LINE(5)

|

||||

/** @} */

|

||||

|

||||

#ifdef __cplusplus

|

||||

}

|

||||

#endif

|

||||

|

||||

#endif /* ARDUINO_PINMAP_H */

|

||||

/** @} */

|

||||

77

boards/p-nucleo-wb55/include/board.h

Normal file

77

boards/p-nucleo-wb55/include/board.h

Normal file

@ -0,0 +1,77 @@

|

||||

/*

|

||||

* Copyright (C) 2019 Inria

|

||||

*

|

||||

* This file is subject to the terms and conditions of the GNU Lesser

|

||||

* General Public License v2.1. See the file LICENSE in the top level

|

||||

* directory for more details.

|

||||

*/

|

||||

|

||||

/**

|

||||

* @ingroup boards_p-nucleo-wb55

|

||||

* @{

|

||||

*

|

||||

* @file

|

||||

* @brief Pin definitions and board configuration options

|

||||

*

|

||||

* @author Francisco Molina <francois-xavier.molina@inria.fr>

|

||||

*/

|

||||

|

||||

#ifndef BOARD_H

|

||||

#define BOARD_H

|

||||

|

||||

#include "board_nucleo.h"

|

||||

|

||||

#ifdef __cplusplus

|

||||

extern "C" {

|

||||

#endif

|

||||

|

||||

/**

|

||||

* @name LED pin definitions and handlers

|

||||

* @{

|

||||

*/

|

||||

#define LED0_PORT GPIOB

|

||||

#define LED0_PIN GPIO_PIN(PORT_B, 5)

|

||||

#define LED0_MASK (1 << 5)

|

||||

#define LED0_ON (LED0_PORT->BSRR = LED0_MASK)

|

||||

#define LED0_OFF (LED0_PORT->BSRR = (LED0_MASK << 16))

|

||||

#define LED0_TOGGLE (LED0_PORT->ODR ^= LED0_MASK)

|

||||

|

||||

#define LED1_PORT GPIOB

|

||||

#define LED1_PIN GPIO_PIN(PORT_B, 0)

|

||||

#define LED1_MASK (1 << 0)

|

||||

#define LED1_ON (LED0_PORT->BSRR = LED1_MASK)

|

||||

#define LED1_OFF (LED0_PORT->BSRR = (LED1_MASK << 16))

|

||||

#define LED1_TOGGLE (LED0_PORT->ODR ^= LED1_MASK)

|

||||

|

||||

#define LED2_PORT GPIOB

|

||||

#define LED2_PIN GPIO_PIN(PORT_B, 1)

|

||||

#define LED2_MASK (1 << 1)

|

||||

#define LED2_ON (LED0_PORT->BSRR = LED2_MASK)

|

||||

#define LED2_OFF (LED0_PORT->BSRR = (LED2_MASK << 16))

|

||||

#define LED2_TOGGLE (LED0_PORT->ODR ^= LED2_MASK)

|

||||

/** @} */

|

||||

|

||||

/* p-nucleo-wb55 always use LED0, as there is no dual use of its pin */

|

||||

#ifndef AUTO_INIT_LED0

|

||||

#define AUTO_INIT_LED0

|

||||

#endif

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name User button

|

||||

* @{

|

||||

*/

|

||||

#define BTN0_PIN GPIO_PIN(PORT_C, 4)

|

||||

#define BTN0_MODE GPIO_IN_PU

|

||||

#define BTN1_PIN GPIO_PIN(PORT_D, 0)

|

||||

#define BTN1_MODE GPIO_IN_PU

|

||||

#define BTN2_PIN GPIO_PIN(PORT_D, 1)

|

||||

#define BTN2_MODE GPIO_IN_PU

|

||||

/** @} */

|

||||

|

||||

#ifdef __cplusplus

|

||||

}

|

||||

#endif

|

||||

|

||||

#endif /* BOARD_H */

|

||||

/** @} */

|

||||

78

boards/p-nucleo-wb55/include/gpio_params.h

Normal file

78

boards/p-nucleo-wb55/include/gpio_params.h

Normal file

@ -0,0 +1,78 @@

|

||||

/*

|

||||

* Copyright (C) 2019 Inria

|

||||

*

|

||||

* This file is subject to the terms and conditions of the GNU Lesser

|

||||

* General Public License v2.1. See the file LICENSE in the top level

|

||||

* directory for more details.

|

||||

*/

|

||||

|

||||

/**

|

||||

* @ingroup boards_p-nucleo-wb55

|

||||

* @{

|

||||

*

|

||||

* @file

|

||||

* @brief Board specific configuration of direct mapped GPIOs

|

||||

*

|

||||

* @author Alexandre Abadie <alexandre.abadie@inria.fr>

|

||||

* @author Francisco Molina <francois-xavier.molina@inria.fr>

|

||||

*

|

||||

*/

|

||||

|

||||

#ifndef GPIO_PARAMS_H

|

||||

#define GPIO_PARAMS_H

|

||||

|

||||

#include "board.h"

|

||||

#include "saul/periph.h"

|

||||

|

||||

#ifdef __cplusplus

|

||||

extern "C" {

|

||||

#endif

|

||||

|

||||

/**

|

||||

* @brief GPIO pin configuration

|

||||

*/

|

||||

static const saul_gpio_params_t saul_gpio_params[] =

|

||||

{

|

||||

#ifdef AUTO_INIT_LED0

|

||||

{

|

||||

.name = "LED(blue)",

|

||||

.pin = LED0_PIN,

|

||||

.mode = GPIO_OUT

|

||||

},

|

||||

#endif

|

||||

{

|

||||

.name = "LED(green)",

|

||||

.pin = LED1_PIN,

|

||||

.mode = GPIO_OUT

|

||||

},

|

||||

{

|

||||

.name = "LED(red)",

|

||||

.pin = LED2_PIN,

|

||||

.mode = GPIO_OUT

|

||||

},

|

||||

{

|

||||

.name = "Button(B1 User)",

|

||||

.pin = BTN0_PIN,

|

||||

.mode = BTN0_MODE,

|

||||

.flags = SAUL_GPIO_INVERTED,

|

||||

},

|

||||

{

|

||||

.name = "Button(B2 User)",

|

||||

.pin = BTN1_PIN,

|

||||

.mode = BTN1_MODE,

|

||||

.flags = SAUL_GPIO_INVERTED,

|

||||

},

|

||||

{

|

||||

.name = "Button(B3 User)",

|

||||

.pin = BTN2_PIN,

|

||||

.mode = BTN2_MODE,

|

||||

.flags = SAUL_GPIO_INVERTED,

|

||||

},

|

||||

};

|

||||

|

||||

#ifdef __cplusplus

|

||||

}

|

||||

#endif

|

||||

|

||||

#endif /* GPIO_PARAMS_H */

|

||||

/** @} */

|

||||

175

boards/p-nucleo-wb55/include/periph_conf.h

Normal file

175

boards/p-nucleo-wb55/include/periph_conf.h

Normal file

@ -0,0 +1,175 @@

|

||||

/*

|

||||

* Copyright (C) 2019 Inria

|

||||

*

|

||||

* This file is subject to the terms and conditions of the GNU Lesser

|

||||

* General Public License v2.1. See the file LICENSE in the top level

|

||||

* directory for more details.

|

||||

*/

|

||||

|

||||

/**

|

||||

* @ingroup boards_p-nucleo-wb55

|

||||

* @{

|

||||

*

|

||||

* @file

|

||||

* @brief Peripheral MCU configuration for the p-nucleo-wb55 board

|

||||

*

|

||||

* @author Francisco Molina <francois-xavier.molina@inria.fr>

|

||||

*/

|

||||

|

||||

|

||||

#ifndef PERIPH_CONF_H

|

||||

#define PERIPH_CONF_H

|

||||

|

||||

#include "periph_cpu.h"

|

||||

#include "cfg_i2c1_pb8_pb9.h"

|

||||

#include "cfg_rtt_default.h"

|

||||

#include "cfg_timer_tim2.h"

|

||||

|

||||

#ifdef __cplusplus

|

||||

extern "C" {

|

||||

#endif

|

||||

|

||||

/**

|

||||

* @name Clock system configuration

|

||||

* @{

|

||||

*/

|

||||

/* 0: no external high speed crystal available

|

||||

* else: actual crystal frequency [in Hz] */

|

||||

#define CLOCK_HSE (32000000U)

|

||||

|

||||

#ifndef CLOCK_LSE

|

||||

/* 0: no external low speed crystal available,

|

||||

* 1: external crystal available (always 32.768kHz)

|

||||

*/

|

||||

#define CLOCK_LSE (1)

|

||||

#endif

|

||||

|

||||

/* 0: enable MSI only if HSE isn't available

|

||||

* 1: always enable MSI (e.g. if USB or RNG is used)*/

|

||||

#define CLOCK_MSI_ENABLE (1)

|

||||

|

||||

#ifndef CLOCK_MSI_LSE_PLL

|

||||

/* 0: disable Hardware auto calibration with LSE

|

||||

* 1: enable Hardware auto calibration with LSE (PLL-mode)

|

||||

*/

|

||||

#define CLOCK_MSI_LSE_PLL (1)

|

||||

#endif

|

||||

|

||||

/* give the target core clock (HCLK) frequency [in Hz], maximum: 64MHz */

|

||||

#define CLOCK_CORECLOCK (64000000U)

|

||||

/* PLL configuration: make sure your values are legit!

|

||||

*

|

||||

* compute by: CORECLOCK = (((PLL_IN / M) * N) / R)

|

||||

* with:

|

||||

* PLL_IN: input clock, HSE or MSI @ 48MHz

|

||||

* M: pre-divider, allowed range: [1:8]

|

||||

* N: multiplier, allowed range: [8:86]

|

||||

* R: post-divider, allowed range: [2:8]

|

||||

*

|

||||

* Also the following constraints need to be met:

|

||||

* (PLL_IN / M) -> [4MHz:16MHz]

|

||||

* (PLL_IN / M) * N -> [64MHz:344MHz]

|

||||

* CORECLOCK -> 64MHz MAX!

|

||||

*/

|

||||

#define CLOCK_PLL_M (4)

|

||||

#define CLOCK_PLL_N (32)

|

||||

#define CLOCK_PLL_R (4)

|

||||

|

||||

/* EXTAHB (HCLK2) max freq 32 Mhz*/

|

||||

#define CLOCK_EXTAHB_DIV RCC_EXTCFGR_C2HPRE_3

|

||||

#define CLOCK_EXTAHB (CLOCK_CORECLOCK / 2)

|

||||

/* peripheral clock setup */

|

||||

#define CLOCK_AHB_DIV 0x00000000U

|

||||

#define CLOCK_AHB (CLOCK_CORECLOCK / 1)

|

||||

#define CLOCK_APB1_DIV 0x00000000U

|

||||

#define CLOCK_APB1 (CLOCK_CORECLOCK / 1)

|

||||

#define CLOCK_APB2_DIV 0x00000000U

|

||||

#define CLOCK_APB2 (CLOCK_CORECLOCK / 1)

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name UART configuration

|

||||

* @{

|

||||

*/

|

||||

static const uart_conf_t uart_config[] = {

|

||||

{

|

||||

.dev = USART1,

|

||||

.rcc_mask = RCC_APB2ENR_USART1EN,

|

||||

.rx_pin = GPIO_PIN(PORT_B, 7),

|

||||

.tx_pin = GPIO_PIN(PORT_B, 6),

|

||||

.rx_af = GPIO_AF7,

|

||||

.tx_af = GPIO_AF7,

|

||||

.bus = APB2,

|

||||

.irqn = USART1_IRQn,

|

||||

.type = STM32_USART,

|

||||

.clk_src = 0, /* Use APB clock */

|

||||

},

|

||||

{

|

||||

.dev = LPUART1,

|

||||

.rcc_mask = RCC_APB1ENR2_LPUART1EN,

|

||||

.rx_pin = GPIO_PIN(PORT_A, 3),

|

||||

.tx_pin = GPIO_PIN(PORT_A, 2),

|

||||

.rx_af = GPIO_AF8,

|

||||

.tx_af = GPIO_AF8,

|

||||

.bus = APB12,

|

||||

.irqn = LPUART1_IRQn,

|

||||

.type = STM32_LPUART,

|

||||

.clk_src = 0, /* Use APB clock */

|

||||

},

|

||||

};

|

||||

|

||||

#define UART_0_ISR (isr_usart1)

|

||||

#define UART_1_ISR (isr_lpuart1)

|

||||

|

||||

#define UART_NUMOF ARRAY_SIZE(uart_config)

|

||||

/** @} */

|

||||

|

||||

/**

|

||||

* @name SPI configuration

|

||||

*

|

||||

* @note The spi_divtable is auto-generated from

|

||||

* `cpu/stm32_common/dist/spi_divtable/spi_divtable.c`

|

||||

* @{

|

||||

*/

|

||||

static const uint8_t spi_divtable[2][5] = {

|

||||

{ /* for APB1 @ 20000000Hz */

|

||||

7, /* -> 78125Hz */

|

||||

5, /* -> 312500Hz */

|

||||

3, /* -> 1250000Hz */

|

||||

1, /* -> 5000000Hz */

|

||||

0 /* -> 10000000Hz */

|

||||

},

|

||||

{ /* for APB2 @ 40000000Hz */

|

||||

7, /* -> 156250Hz */

|

||||

6, /* -> 312500Hz */

|

||||

4, /* -> 1250000Hz */

|

||||

2, /* -> 5000000Hz */

|

||||

1 /* -> 10000000Hz */

|

||||

}

|

||||

};

|

||||

|

||||

static const spi_conf_t spi_config[] = {

|

||||

{

|

||||

.dev = SPI1,

|

||||

.mosi_pin = GPIO_PIN(PORT_A, 7),

|

||||

.miso_pin = GPIO_PIN(PORT_A, 6),

|

||||

.sclk_pin = GPIO_PIN(PORT_A, 5),

|

||||

.cs_pin = GPIO_UNDEF,

|

||||

.mosi_af = GPIO_AF5,

|

||||

.miso_af = GPIO_AF5,

|

||||

.sclk_af = GPIO_AF5,

|

||||

.cs_af = GPIO_AF5,

|

||||

.rccmask = RCC_APB2ENR_SPI1EN,

|

||||

.apbbus = APB2,

|

||||

}

|

||||

};

|

||||

|

||||

#define SPI_NUMOF ARRAY_SIZE(spi_config)

|

||||

/** @} */

|

||||

|

||||

#ifdef __cplusplus

|

||||

}

|

||||

#endif

|

||||

|

||||

#endif /* PERIPH_CONF_H */

|

||||

/** @} */

|

||||

Loading…

Reference in New Issue

Block a user